C-DeviceとPLL(ICS525-02)の接続テスト

REXには250MHzまでのクロックを生成できるPLLデバイス

ICS525-02 が実装されています。C-Devの出力ピンを用いてICS525-02 を制御することで、必要とするクロックを生成します。

C-Dev のコンフィギュレーション・テストとして、20MHz のクロックを生成する方法を説明します。

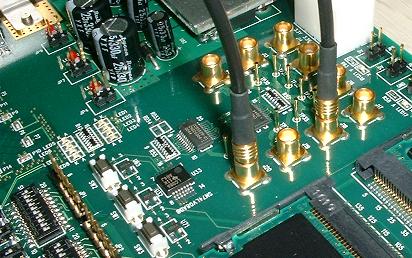

REX上のC-Dev(中央)とICS525-02(右上)

ハードウェアとREX上のスイッチの設定

(1) REX上のスイッチを以下の様に設定する。

SW7(1,2,3,4という順で) ON ON ON OFF

SW4: ON OFF OFF OFF OFF OFF ON OFF OFF OFF

SW5: ON OFF OFF OFF OFF OFF ON OFF OFF OFF

S1: ON(右側)

S5: ON(右側)

S2: ON(上側)

S3: ON

S4: ON

S6: ON

S7: ON

S8: ON

SW6: OFF OFF OFF OFF OFF OFF OFF OFF *これを変更することでクロック周波数が変わる。*

(2) REXのソケットにコンフィギュレーションROM XC18V02 を取り付ける。

(3) REXのJP3にダウンロードケーブルを接続する。

(4)クロックケーブルを接続する。J20とJ12~J19のひとつとの間を接続

(5)電源を供給する。

J20 と J18 をクロックケーブルで接続することで C-Dev と ICS525 を接続できる。

ICS525-02 OSCaR

以下の式によって、必要とするクロックを生成します。REXの場合には、Input frequency は 8MHz です。

Clk frequency = Input frequency x 2 x (VDW +

8 ) / (RDW + 2)(OD)

Where

RDW(Reference Divider Word) = o to 127

VDW(VCO Divider Word) = 0 to 511

OD(Output Divider) = values on page 3 of the mannual.

次のURLに必要とする周波数を入力すれば、必要とするピン設定を表示してくれます。http://www.icst.com/products/ics525inputForm.html

詳細はマニュアル http://www.icst.com/pdf/ics5250102.pdf を参考にしてください。

回路仕様

8MHz の固定クロックとICS525により生成されるクロックの2系統により、インクリメントするカウンタを作成し、それぞれの周期でLEDを点滅させる回路を実装します

LED1とLED2は、8MHz のクロックに同期して、8000000クロック毎に(つまり1秒間隔で)カウントアップします。

LED2とLED3は、ICS525が生成したクロックに同期して、30000000クロック毎に(つまり、30MHz のときが1秒間隔)カウントアップします。

SW6の8ビットを、ICS525の入力として接続します。 SW6 がすべてOFFの時に 8MHz、SW6 の8ビットの値を N とすると、8 + N MHz

のクロックを生成します。

Verilog-HDLによる記述と、ピン割り当てファイルを用意する。

top.v

top.ucf

論理合成とコンフィギュレーションに関しては、C-Deviceのコンフィギュレーション・テスト を参考にしてください。

This page is written by Kenji KISE. 2001 7/17