P-Deviceのコンフィギュレーション・テスト

P-Dev のコンフィギュレーションのテストとして、4つのLEDを点滅させる回路を実装する方法を説明します。

ハードウェアとREX上のスイッチの設定

(1) REX上のスイッチを以下の様に設定する。

SW7(1,2,3,4という順で) ON ON ON OFF

SW4: ON OFF OFF OFF OFF OFF ON OFF OFF OFF

SW5: ON OFF OFF OFF OFF OFF ON OFF OFF OFF

S1: ON(右側)

S5: ON(右側)

S2: ON(上側)

S3: ON

S4: ON

S6: ON

S7: ON

S8: ON

SW6: OFF OFF OFF OFF OFF OFF OFF OFF

(2) REXのJP1にダウンロードケーブルを接続する。

(3)電源を供給する。

REX上のJP1にJTAGダウンロードケーブルを接続

ソフトウェアの設定と作業

P-Dev(bottom)には8MHzのクロックが入っています。また、REX上の5つのLED(LED9からLED12)を制御できます。

次に示す Verilog-HDLを用いた記述と、ピン割り当てファイルを用意します。

top.v

top.ucf

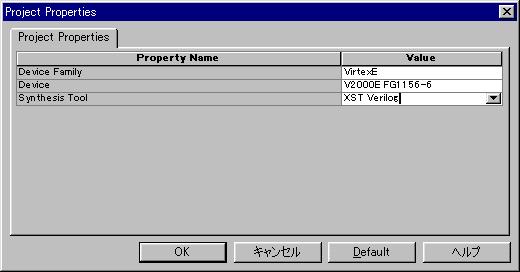

プロジェクトナビゲータを起動して新しいプロジェクトを作成します。プロジェクトのプロパティにおいて、VirtexE, V2000E FG1156-6, XST Verilog を選択します。Verilog-HDL ではなく、VHDL を利用する場合には、XST VHDL を選択します。

作成したプロジェクトのフォルダ内に、 top.v top.ucf

という2つのファイルをコピーし、Project->Add source を選択して top.v をプロジェクトに追加する。

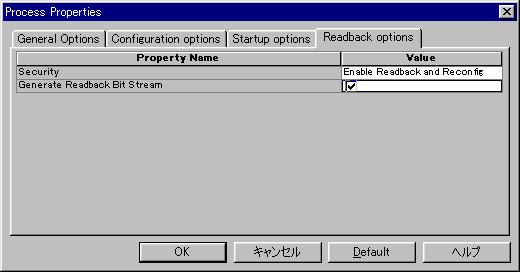

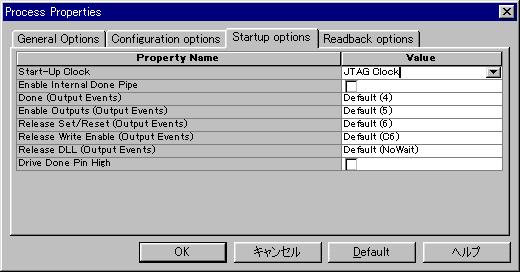

論理合成をおこなう前に、下の2つの写真にあるように Process Properties を変更する。

(1) Create Programming File > Properties > // Readback Options > Generate Readback

Bit Stream にチェックを入れる。(2) Create Programming File > Properties > // Startup Options

> Start-Up Clock を JTAG Clock に変更する。

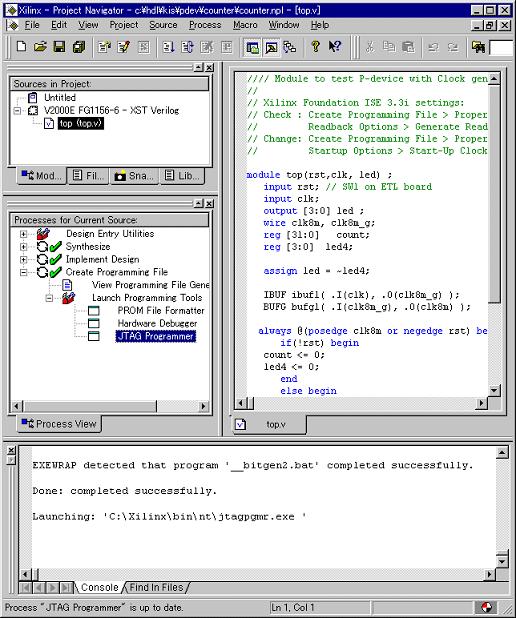

プロジェクトナビゲータの Create Programming

File を選択して、Process -> Run を実行し、コンパイルエラーが発生しないことを確認する。

ここで、エラーが発生した場合にはハードウェア記述にエラーがある可能性がある。ログを見て、ソースコードを確認する。

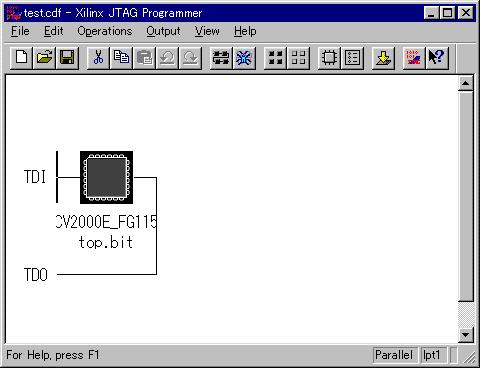

プロジェクトナビゲータから、JTAG Programmer を起動する。 JTAG Programmer の Initialize Chain ボタンを押すことで、下に示すようにJTAGで接続されたデバイスが自動認識される。ただし、ボタンを押す前にREXの電源を入れ、JTAGケーブルを接続しておく必要がある。この時点で、デバイスが認識されていない場合には、JTAGケーブルの接続と、ボードの電源を確認する。

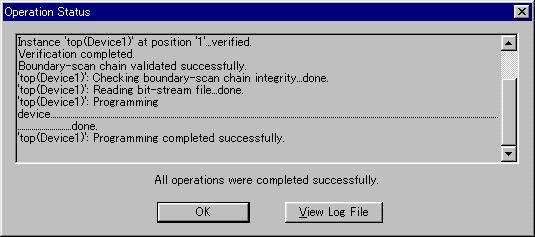

コンフィギュレーションのためのビットファイル top.bit を選択し、Operations -> Progaram を選択し、デバイスのコンフィギュレーションを実行する。

約2分ほど経過すると、上の図のように Programming

completed successfully. が表示され、コンフィギュレーション成功。

0.5秒間隔でLED9からLED12が点灯する。

This page is written by Kenji KISE. 2001 7/16