## 計算機アーキテクチャ 第二 (O)

### RISC vs. CISC RISC命令セットの例とその動作

1

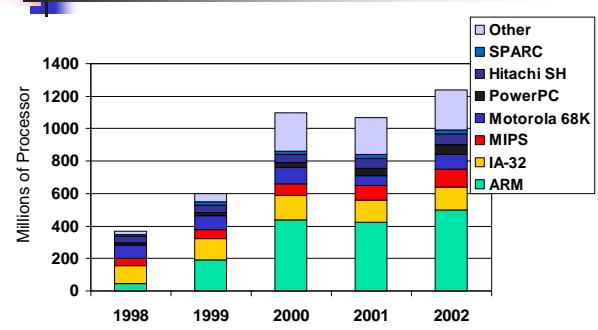

### Instruction Set Architecture (ISA) Type Sales

2

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

### RISC - Reduced Instruction Set Computer

- RISC philosophy**

- fixed instruction lengths

- load-store instruction sets

- limited addressing modes

- limited operations

- Sun SPARC, HP PA-RISC, IBM PowerPC, Compaq Alpha, **MIPS**, ...

*Design goals: speed, cost (design, fabrication, test, packaging), size, power consumption, reliability, memory space (embedded systems)*

3

### MIPS R3000 Instruction Set Architecture (ISA)

- Instruction Categories

- Computational

- Load/Store

- Jump and Branch

- Floating Point

- coprocessor

- Memory Management

- Special

|           |

|-----------|

| Registers |

| R0 - R31  |

| PC        |

| HI        |

| LO        |

#### 3 Instruction Formats: all 32 bits wide

|    |    |             |           |    |       |          |

|----|----|-------------|-----------|----|-------|----------|

| OP | rs | rt          | rd        | sa | funct | R format |

| OP | rs | rt          | immediate |    |       | I format |

| OP |    | jump target |           |    |       | J format |

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

4

### MIPS Arithmetic Instructions

- MIPS assembly language **arithmetic statement**

```

add $t0, $s1, $s2

sub $t0, $s1, $s2

```

- Each arithmetic instruction performs only **one** operation

- Each arithmetic instruction fits in 32 bits and specifies exactly **three** operands

destination  $\leftarrow$  source1 **op** source2

- Operand order is fixed (destination first)

- Those operands are **all** contained in the datapath's **register file** ( $\$t0, \$s1, \$s2$ ) – **indicated by \$**

5

### MIPS Register Convention, ABI (Application Binary Interface)

| Name        | Register Number | Usage                        | Preserve on call? |

|-------------|-----------------|------------------------------|-------------------|

| \$zero      | 0               | <b>constant 0 (hardware)</b> | n.a.              |

| \$at        | 1               | reserved for assembler       | n.a.              |

| \$v0 - \$v1 | 2-3             | returned values              | no                |

| \$a0 - \$a3 | 4-7             | <b>arguments</b>             | yes               |

| \$t0 - \$t7 | 8-15            | temporaries                  | no                |

| \$s0 - \$s7 | 16-23           | saved values                 | yes               |

| \$t8 - \$t9 | 24-25           | temporaries                  | no                |

| \$gp        | 28              | global pointer               | yes               |

| \$sp        | 29              | stack pointer                | yes               |

| \$fp        | 30              | frame pointer                | yes               |

| \$ra        | 31              | return addr (hardware)       | yes               |

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

6

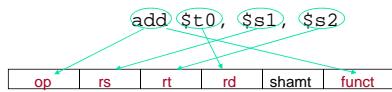

## Machine Language - Add Instruction

- Instructions, like registers and words of data, are **32 bits long**

- Arithmetic Instruction Format (R format):

op 6-bits **opcode** that specifies the operation

rs 5-bits **register file address** of the first **source operand**

rt 5-bits **register file address** of the second **source operand**

rd 5-bits **register file address** of the result's **destination**

shamt 5-bits **shift amount** (for shift instructions)

funct 6-bits **function code** augmenting the opcode

7

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習

- $f = (g + h) - (i + j)$

$f, g, h, i, j$  をそれぞれレジスタ  $\$s0, \$s1, \$s2, \$s3, \$s4$  に割り付けるとする。

上のステートメントをコンパイルした結果のMIPSアプリケーション・コードはどうなるか。

8

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習 (参考書 48ページ)

- $f = (g + h) - (i + j)$

$f, g, h, i, j$  をそれぞれレジスタ  $\$s0, \$s1, \$s2, \$s3, \$s4$  に割り付けるとする。

上のステートメントをコンパイルした結果のMIPSアプリケーション・コードはどうなるか。

```

add $t0, $s1, $s2    # $t0 = (g + h)

add $t1, $s3, $s4    #

sub $s0, $t0, $t1    #

```

9

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

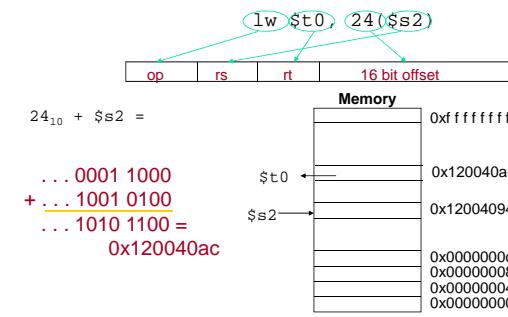

## Machine Language - Load Instruction

- Load/Store Instruction Format (I format):

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## MIPS Memory Access Instructions

- MIPS has two basic **data transfer** instructions for accessing memory

- lw \$t0, 4(\$s3) #load word from memory

- sw \$t0, 8(\$s3) #store word to memory

- The data is loaded into (lw) or stored from (sw) a register in the register file – a 5 bit address

- The memory address – a 32 bit address – is formed by adding the contents of the **base address register** to the **offset** value

- A 16-bit field meaning access is limited to memory locations within a region of  $\pm 2^{13}$  or 8,192 words ( $\pm 2^{15}$  or 32,768 bytes) of the address in the base register

- Note that the offset can be positive or negative

11

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習

- $g = h + A[8]$

100語からなる配列Aがあるとする。また、コンパイラは変数  $g, h$  にレジスタ  $\$s1, \$s2$  を割り付ける。さらに配列の開始アドレスは  $\$s3$  に納められているとする。

上のステートメントをコンパイルせよ。

12

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習（参考書 50ページ）

## 演習

---

- $A[12] = h + A[8]$

100語から成る配列Aがあるとする。また、コンパイラは変数g, h にレジスタ \$s1, \$s2 を割り付ける。さらに配列の開始アドレスは \$s3 に納められているとする。

上のステートメントをコンパイルせよ。

Adapted from: Computer Organization and Design, Patterson & Hennessy, © 2005.

14

## 演習（参考書 51ページ）

## MIPS Control Flow Instructions

## More Branch Instructions

## More Branch Instructions, Con't

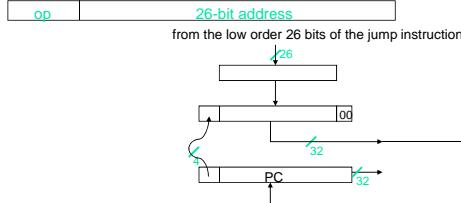

## Other Control Flow Instructions

- MIPS also has an **unconditional branch** instruction or **jump** instruction:

**j label #go to label**

- Instruction Format (**J** Format):

19

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Aside: Branching Far Away

- What if the branch destination is further away than can be captured in 16 bits?

- The assembler comes to the rescue – it inserts an unconditional jump to the branch target and inverts the condition

**beq \$s0, \$s1, L1**

becomes

**bne \$s0, \$s1, L2**

**j L1**

**L2:**

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

20

## Instructions for Accessing Procedures

- MIPS **procedure call** instruction:

**jal ProcedureAddress #jump and link**

- Saves PC+4 in register **\$ra** to have a link to the next instruction for the procedure return

- Machine format (**J** format):

21

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## MIPS Immediate Instructions

- Small constants are used often in typical code

- Possible approaches?

- put “typical constants” in memory and load them

- create hard-wired registers (like \$zero) for constants like 1

- have special instructions that contain constants !

**addi \$sp, \$sp, 4 #\$sp = \$sp + 4**

**slti \$t0, \$s2, 15 #\$t0 = 1 if \$s2 < 15**

- Machine format (**I** format):

- The constant is kept **inside** the instruction itself!

- Immediate format **limits** values to the range  $+2^{15}-1$  to  $-2^{15}$

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

22

## MIPS ISA So Far

| Category                       | Instr                      | Op Code  | Example              | Meaning                             |

|--------------------------------|----------------------------|----------|----------------------|-------------------------------------|

| Arithmetic<br>(R & I format)   | add                        | 0 and 32 | add \$s1, \$s2, \$s3 | \$s1 = \$s2 + \$s3                  |

|                                | subtract                   | 0 and 34 | sub \$s1, \$s2, \$s3 | \$s1 = \$s2 - \$s3                  |

|                                | add immediate              | 8        | addi \$s1, \$s2, 6   | \$s1 = \$s2 + 6                     |

|                                | or immediate               | 13       | ori \$s1, \$s2, 6    | \$s1 = \$s2   6                     |

| Data Transfer<br>(I format)    | load word                  | 35       | lw \$s1, 24(\$s2)    | \$s1 = Memory(\$s2+24)              |

|                                | store word                 | 43       | sw \$s1, 24(\$s2)    | Memory(\$s2+24) = \$s1              |

|                                | load byte                  | 32       | lb \$s1, 25(\$s2)    | \$s1 = Memory(\$s2+25)              |

|                                | store byte                 | 40       | sb \$s1, 25(\$s2)    | Memory(\$s2+25) = \$s1              |

|                                | load upper imm             | 15       | lui \$s1, 6          | \$s1 = 6 * 2 <sup>16</sup>          |

| Cond. Branch<br>(I & R format) | br on equal                | 4        | beq \$s1, \$s2, L    | If (\$s1 == \$s2) go to L           |

|                                | br on not equal            | 5        | bne \$s1, \$s2, L    | If (\$s1 != \$s2) go to L           |

|                                | set on less than           | 0 and 42 | slt \$s1, \$s2, \$s3 | If (\$s2 < \$s3) \$s1=1 else \$s1=0 |

|                                | set on less than immediate | 10       | slti \$s1, \$s2, 6   | If (\$s2 < 6) \$s1=1 else \$s1=0    |

| Uncond. Jump<br>(J & R format) | jump                       | 2        | j 2500               | go to 10000                         |

|                                | jump register              | 0 and 8  | jr \$t1              | go to \$t1                          |

|                                | jump and link              | 3        | jal 2500             | go to 10000: \$ra=PC+4              |

23

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## MIPS Register Convention, ABI (Application Binary Interface)

| Name        | Register Number | Usage                        | Preserve on call? |

|-------------|-----------------|------------------------------|-------------------|

| \$zero      | 0               | <b>constant 0 (hardware)</b> | n.a.              |

| \$at        | 1               | reserved for assembler       | n.a.              |

| \$v0 - \$v1 | 2-3             | returned values              | no                |

| \$a0 - \$a3 | 4-7             | <b>arguments</b>             | yes               |

| \$t0 - \$t7 | 8-15            | temporaries                  | no                |

| \$s0 - \$s7 | 16-23           | saved values                 | yes               |

| \$t8 - \$t9 | 24-25           | temporaries                  | no                |

| \$gp        | 28              | global pointer               | yes               |

| \$sp        | 29              | stack pointer                | yes               |

| \$fp        | 30              | frame pointer                | yes               |

| \$ra        | 31              | return addr (hardware)       | yes               |

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

24

## ABI Sample

```

int simple_add(int a, int b)

{

return a + b;

}

```

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

25

## ABI Sample

```

int simple_add(int a, int b)

{

return a + b;

}

```

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

26

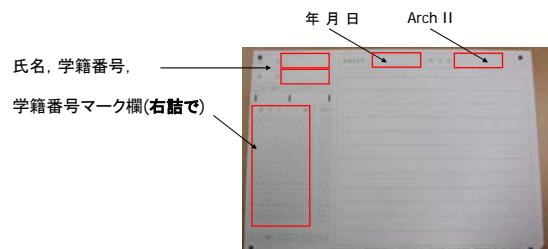

## スキャネットシート

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

27

## Exercise

```

swap(int v[], int k)

{

int temp:

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

```

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

28

## Exercise 1

```

swap(int v[], int k)

{

int temp:

temp = v[k];

v[k] = v[k+1];

v[k+1] = temp;

}

swap:

add $t1, $a1, $a1 # $t1 = k * 4;

add $t1, $t1, $t1 # $t1 = &v[k];

lw $t0, 0($t1) # $t0 = v[k];

lw             #

sw             #

sw             #

jr $ra         # return

```

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

sll \$t1, \$a1, 2

29

## CISC - Complex Instruction Set Computer

- **CISC philosophy**

- ! fixed instruction lengths

- ! load-store instruction sets

- ! limited addressing modes

- ! limited operations

- DEC VAX11 Intel 80x86, ...

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

30

## アナウンス

- 講義スライド, 講義スケジュール

- [www.arch.cs.titech.ac.jp](http://www.arch.cs.titech.ac.jp)

- MIPS/SPIM Reference Cardは次回も利用します.

31

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005