2012-07-12 2012年 前学期 TOKYO TECH

# 計算機アーキテクチャ 第一 (E)

## 磁気ディスク, RAID

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

### Acknowledgement

- Lecture slides for Computer Organization and Design, Third Edition, courtesy of Professor Mary Jane Irwin, Penn State University

- Lecture slides for Computer Organization and Design, third edition, Chapters 1-9, courtesy of Professor Tod Amon, Southern Utah University.

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

2

### TSUBAME 2.0

TSUBAME2では上段のとおり複数の計算ノードを採用していますが、そのほとんどは54GB のRAMを搭載したThinノードです。共有メモリとして54GB以上用いる場合の場合は、古い最新GPUを搭載したThinノードを用意しています。Thinノードの計算性能はCPU+GPU共に倍速で15GFlops(アーティファクト時)、GPUのみで15.5GFlopsです(CPU+GPU共に倍速度浮動小数点演算性能)。またモデルAノードはCPU用の2CPU合算で64GB/s、GPU用が3基合算で462GB/sになります。それぞれハイエンドが出て、もはや理論データ性能であり実際のアプリケーションでの性能はこれに劣りますが、TSUBAME2ではCPU性能に比べてGPU性能を重視した構成となっています。

ストレージ

TSUBAME2ではストレージ機能としてホームディレクトリを提供するホーム領域と大規模データ処理用並列ファイルシステム領域の2種類のストレージ機能が利用可能であり、さらにデータドライブによる階層キャッシングによる障害対策がとられています。

| ストレージ種別      | 用途                                                               | プロトコル            | 構成                                                                                            | マウント先  |

|--------------|------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|--------|

| ホーム          | 計算ノードのホームディレクトリ用 (NFS), 学内ストレージサービス (CIFS), 学内オペティングサービス (iSCSI) | NFS, CIFS, iSCSI | BlueArc Mercury 100 (一部GRIDScalar)                                                            | /home  |

| 並列ファイルシステム領域 | 大規模データ処理用、実行時の中間データなどのためのスクラッチ領域                                 | Lustre           | MDS: HP DL360 G6 x 6, OSS: HP DL360 G6 x 20, DON SFA 10K x 3, 2TB SATA x 3550, 600GB SAS x 50 | /gscr0 |

|              |                                                                  | GPFS             |                                                                                               | /data0 |

3

### RAID: Disk Arrays

#### Redundant Array of Inexpensive Disks

- Arrays of small and inexpensive disks

- Increase potential **throughput** by having many disk drives

- Data is spread over multiple disk

- Multiple accesses are made to several disks at a time

- Reliability** is lower than a single disk

- But **availability** can be improved by adding **redundant disks (RAID)**

4

### RAID: Level 0 (RAID 0, 冗長性なし, ストライピング)

- Multiple smaller disks as opposed to **one big disk**

- Spreading the blocks over multiple disks – **striping** – means that multiple blocks can be accessed in parallel increasing the performance

- 4 disk system gives four times the throughput of a 1 disk system

- Same cost as **one big disk** – assuming 4 small disks cost the same as one big disk

- No redundancy, so what if one disk fails?

5

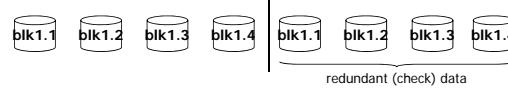

### RAID: Level 1 (Redundancy via Mirroring)

- Uses twice as many disks for redundancy so there are always two copies of the data

- The number of redundant disks = the number of data disks so twice the **cost of one big disk**

- writes have to be made to both sets of disks, so writes would be only 1/2 the performance of RAID 0

- What if one disk fails?

- If a disk fails, the system just goes to the “**mirror**” for the data

6

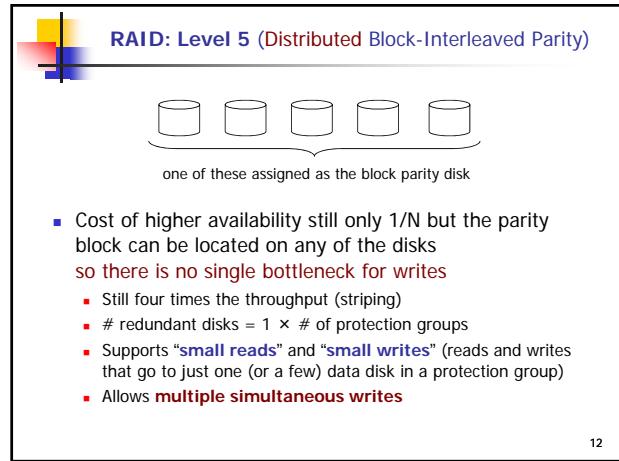

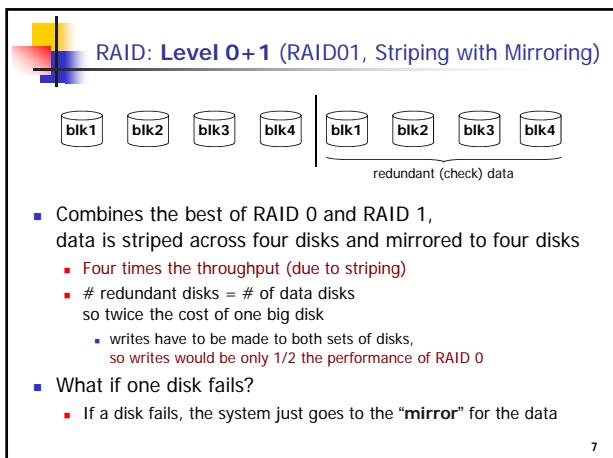

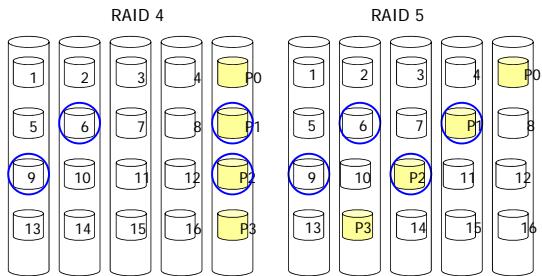

## Distributing Parity Blocks

- By distributing parity blocks to all disks, some small writes can be performed **in parallel**

13

## Disk and RAID Summary

- Four components of disk access time:

- Seek Time: advertised to be 3 to 14 ms but lower in real systems

- Rotational Latency: 5.6 ms at 5400 RPM and 2.0 ms at 15000 RPM

- Transfer Time: 30 to 80 MB/s

- Controller Time: typically less than .2 ms

- RAIDS can be used to improve availability

- RAID 0 and RAID 5 – widely used in servers, one estimate is that 80% of disks in servers are RAID

- RAID 1 (mirroring) – EMC, Tandem, IBM

- RAID 4 – Network Appliance

- RAIDs have enough redundancy to allow continuous operation

14

## Exercise

- 磁気ディスク(ハードディスク)の信頼性を向上させる技術 RAID(Redundant Array of Inexpensive Disks)がある。5台ハードディスクの中の1台をパリティとして用いるRAID-4の構成を示せ。また、このシステムでデータが破壊される典型的な例を議論せよ。

- mean time to failure (MTTF), mean time to repair (MTTR)を用いて、アベイラビリティの式を示せ。先のRAID-4のアベイラビリティを向上させるために、有効な手段を述べよ。

氏名、学籍番号、

学籍番号マーク欄

15

2012-07-12

2012年 前学期 TOKYO TECH

## 計算機アーキテクチャ 第一 (E)

### 仮想記憶

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

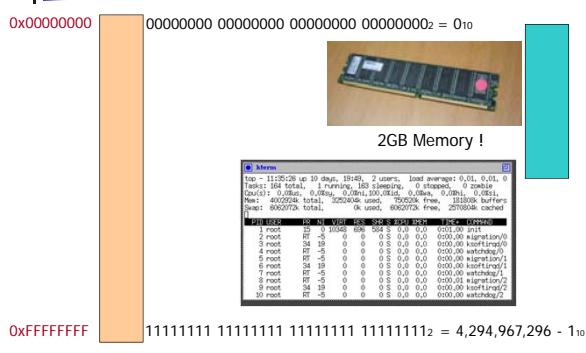

## 例: 32ビット(4GB)のメモリ空間

17

## Virtual Memory (仮想記憶)

- Use main memory as a “cache” for secondary memory

- Provides the ability to easily run programs **larger** than the size of physical memory

- Simplifies** loading a program for execution by providing for code relocation (i.e., the code can be loaded anywhere in main memory)

- Allows efficient and safe sharing of memory among **multiple** programs

Secondary memory (disk)

18

## Virtual Memory (仮想記憶)

- What makes it work? – again the **Principle of Locality**

- A program is likely to access a **relatively small portion** of its address space during any period of time

19

## Virtual Memory (仮想記憶)

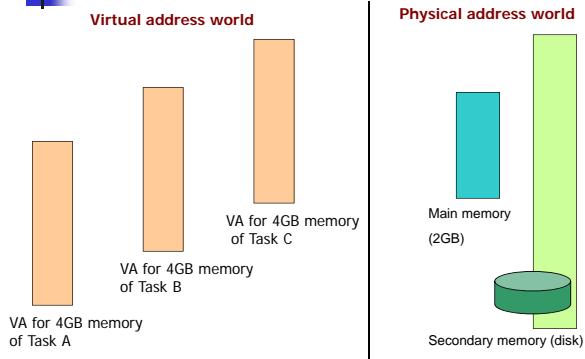

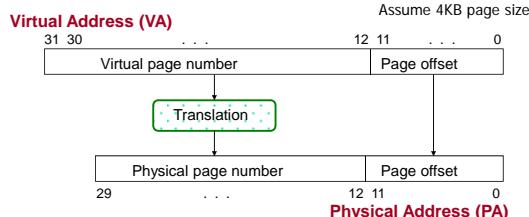

- Each program is compiled into its own address space – a “**virtual address (VA)**” space

- Physical address (PA)** for the access of physical devices

- During run-time each **virtual address, VA** (仮想アドレス) must be translated to a **physical address, PA** (物理アドレス)

20

## Virtual Memory (仮想記憶)

21

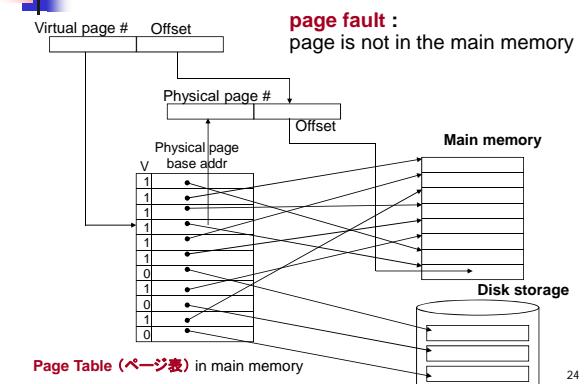

## Two Programs Sharing Physical Memory

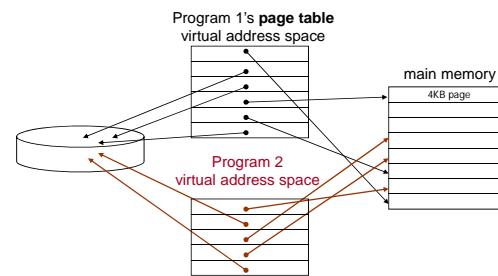

- A program’s address space is divided into **pages** (all one fixed size) or **segments** (variable sizes)

- The starting location of each page (either in **main memory** or in **secondary memory**) is contained in the program’s **page table**

22

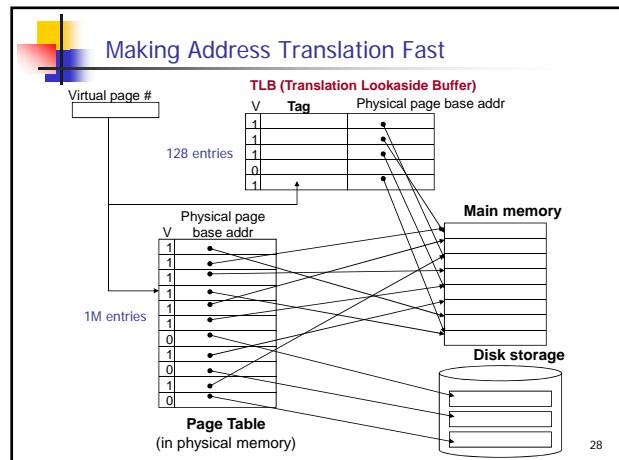

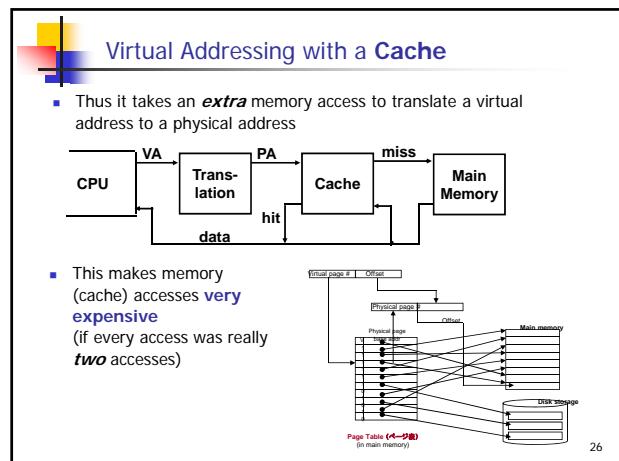

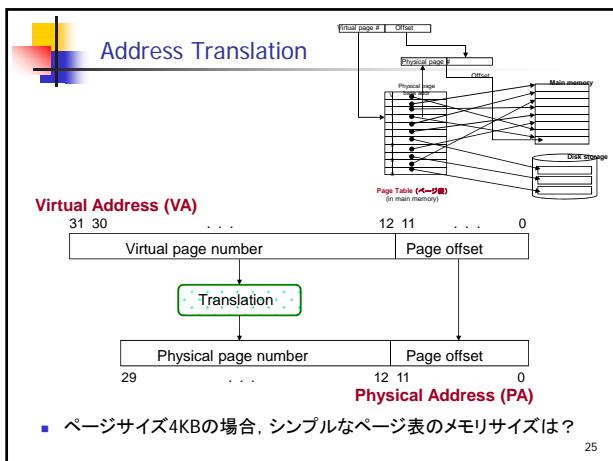

## Address Translation

- A virtual address is translated to a physical address by a combination of hardware and software

23

## Address Translation Mechanisms

24

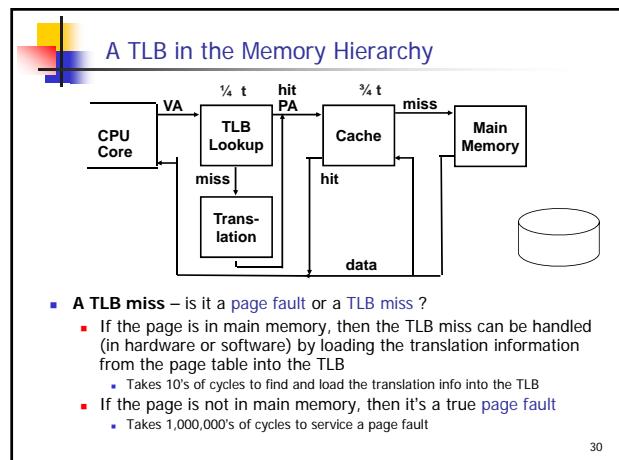

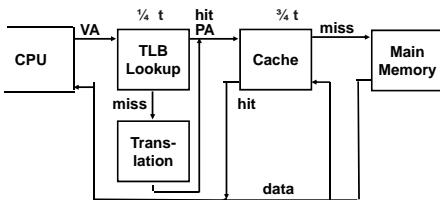

### A TLB in the Memory Hierarchy

- **page fault** : page is not in physical memory

- **TLB misses** are much more frequent than true page faults

31

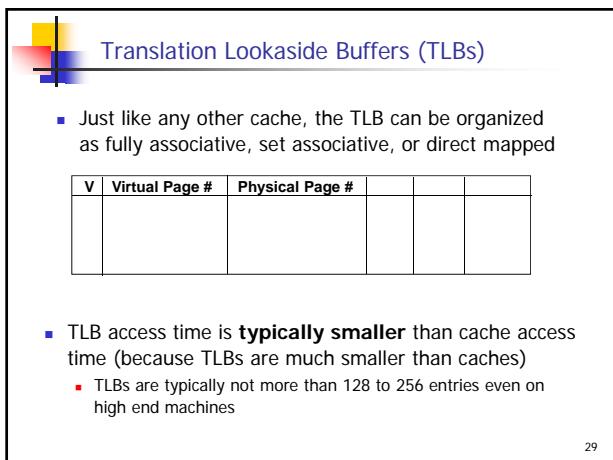

### Two Machines' TLB Parameters

|                  | Intel P4                                                                                                                                                        | AMD Opteron                                                                                                                                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLB organization | 1 TLB for instructions and 1 TLB for data<br>Both 4-way set associative<br>Both use ~LRU replacement<br>Both have 128 entries<br>TLB misses handled in hardware | 2 TLBs for instructions and 2 TLBs for data<br>Both L1 TLBs fully associative with ~LRU replacement<br>Both L2 TLBs are 4-way set associative with round-robin LRU<br>Both L1 TLBs have 40 entries<br>Both L2 TLBs have 512 entries<br>TLB misses handled in hardware |

32

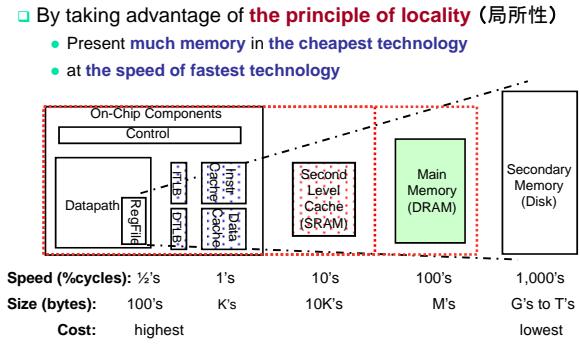

### A Typical Memory Hierarchy

33

### The Hardware/Software Boundary

- What parts of the virtual to physical address translation is done by or assisted by the hardware?

- **Translation Lookaside Buffer (TLB)** that caches the recent translations

- TLB access time is part of the cache hit time

- May cause an extra stage in the pipeline for TLB access

- Page table storage, fault detection and updating

- **Page faults** result in **interrupts (precise)** that are then handled by the **OS**

- Hardware must support (i.e., update appropriately) **Dirty** and **Reference bits** (e.g., ~LRU) in the Page Tables

34

### アナウンス

- 講義スライドおよびスケジュール

- [www.arch.cs.titech.ac.jp](http://www.arch.cs.titech.ac.jp)

- 講義日程が変更になることがあるので頻繁に確認すること。

35

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005