## 計算機アーキテクチャ 第一 (E)

### メモリ1:半導体メモリシステム

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

## Acknowledgement

- Lecture slides for Computer Organization and Design, Third Edition, courtesy of Professor Mary Jane Irwin, Penn State University

- Lecture slides for Computer Organization and Design, third edition, Chapters 1-9, courtesy of Professor Tod Amon, Southern Utah University.

2

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

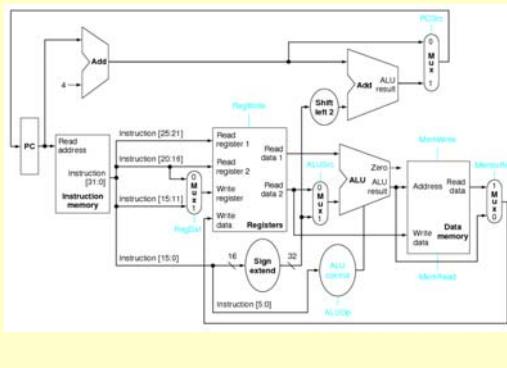

### プロセッサのデータパス(シングル・サイクル)

3

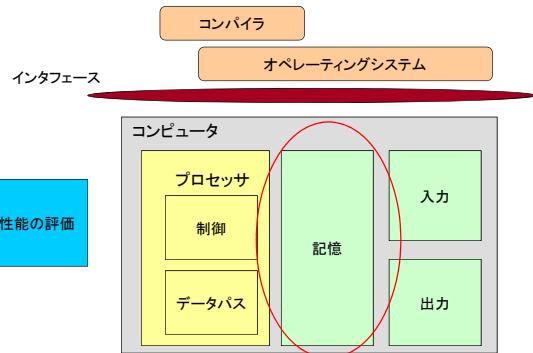

### コンピュータ(ハードウェア)の古典的な要素

4

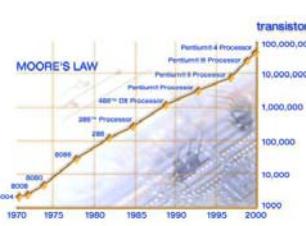

### ムーアの法則によるトランジスタ数の増加

#### ムーアの法則

チップで利用できるトランジスタの数は2年間で2倍に増加する。

| プロセッサ                 | 出荷年  | トランジスタ数    |

|-----------------------|------|------------|

| 4004                  | 1971 | 2,250      |

| 8008                  | 1972 | 2,500      |

| 8080                  | 1974 | 5,000      |

| 8086                  | 1978 | 29,000     |

| 286                   | 1982 | 120,000    |

| 386™ processor        | 1985 | 275,000    |

| 486™ DX processor     | 1989 | 1,180,000  |

| Pentium® processor    | 1993 | 3,100,000  |

| Pentium II processor  | 1997 | 7,500,000  |

| Pentium III processor | 1999 | 24,000,000 |

| Pentium 4 processor   | 2000 | 42,000,000 |

ムーアの法則に従ってトランジスタ数が増加してきた。今後も同様の増加が見込まれる。

出典: Intel社, <http://www.intel.com/research/silicon/mooreslaw.htm>

5

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

### Moore's Law

6

1

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

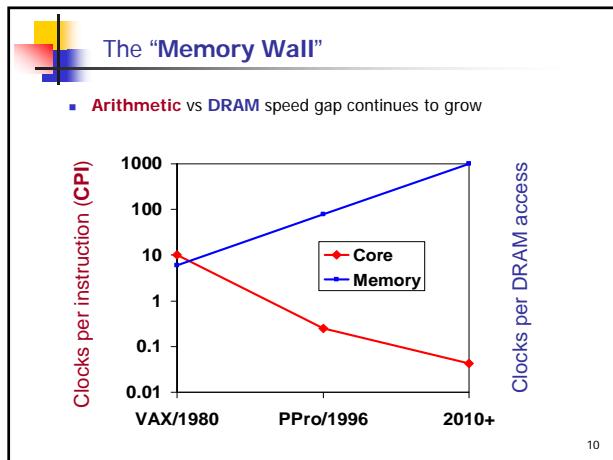

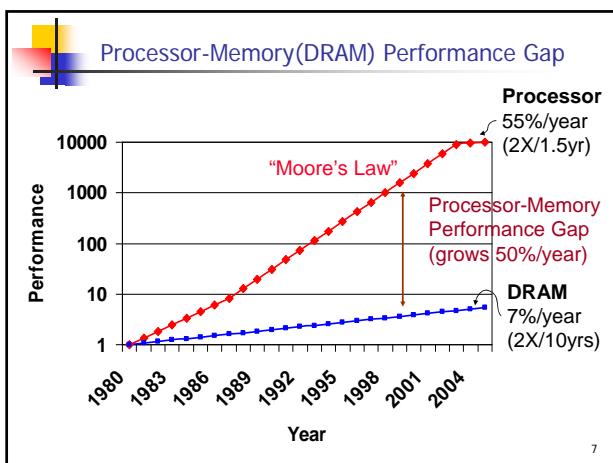

## DRAM (dynamic random access memory)

13

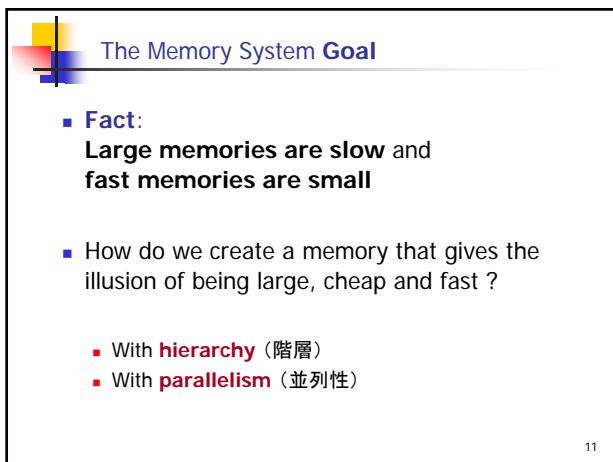

## Cache

- Cache memory consists of a small, fast memory that acts as a buffer for the large memory.

- The nontechnical definition of *cache* is a safe place for hiding things.

Intel Core 2 Duo

14

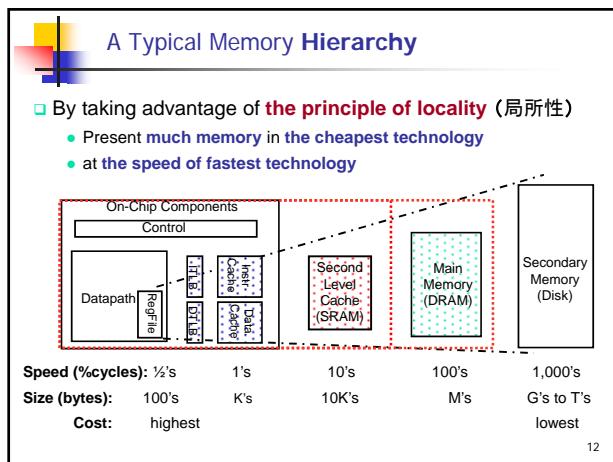

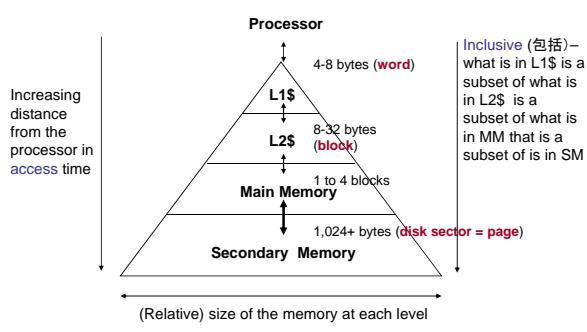

## Characteristics of the Memory Hierarchy

## Memory Hierarchy Technologies

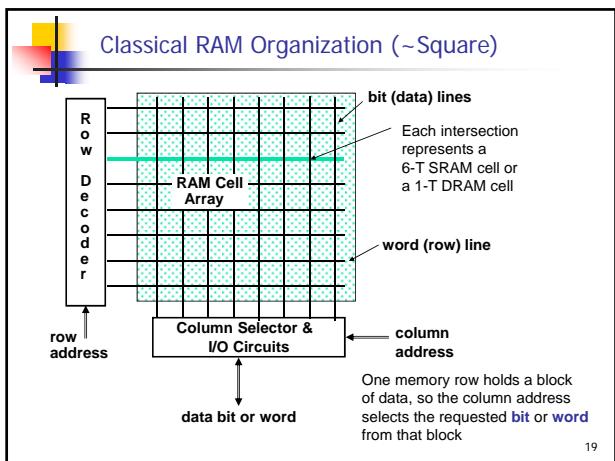

- Caches use **SRAM** (static random access memory) for speed and technology compatibility

- Low density** (6 transistor cells), high power, expensive, fast

- Static**: content will last "forever" (until power turned off)

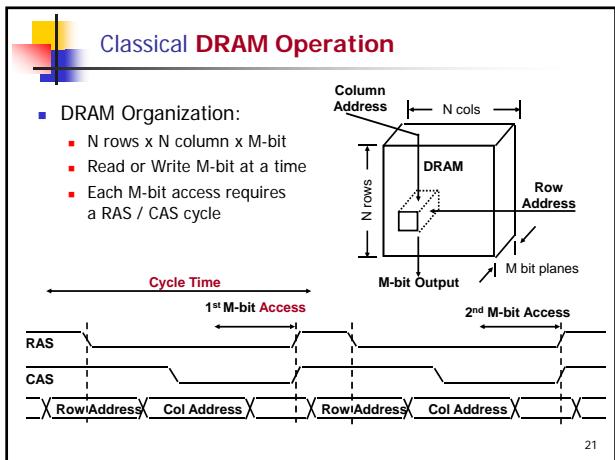

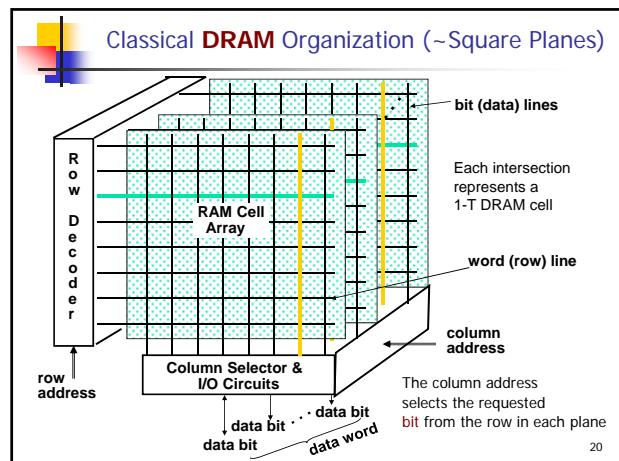

- Main Memory uses **DRAM** for size (density)

- High density** (1 transistor cells), low power, cheap, slow

- Dynamic**: needs to be "refreshed" regularly (~ every 8 ms)

- Addresses divided into 2 halves (row and column)

- RAS** or Row Access Strobe triggering row decoder

- CAS** or Column Access Strobe triggering column selector

16

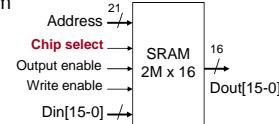

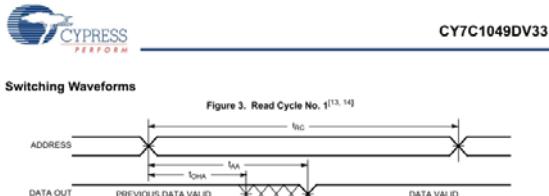

## 非同期式 SRAMメモリ

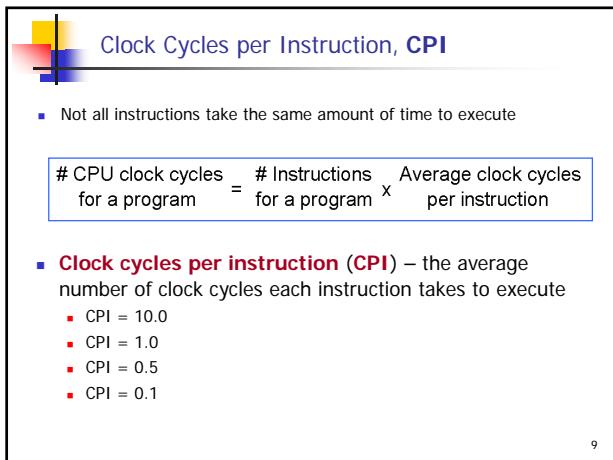

## Memory Performance Metrics

- Latency (レイテンシ, 応答時間):** Time to access one word

- Cycle time:** time between requests

- Access time:** time between the request and when the data is available (or written)

- Usually **cycle time > access time**

- Bandwidth (バンド幅, スループット):** How much data from the memory can be supplied to the processor per unit time

- width of the data channel \* the rate at which it can be used

18