2012-05-24

2012年 前学期 TOKYO TECH

## 計算機アーキテクチャ 第一 (E)

### 5. プロセッサの構成

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

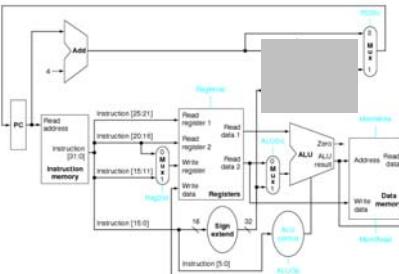

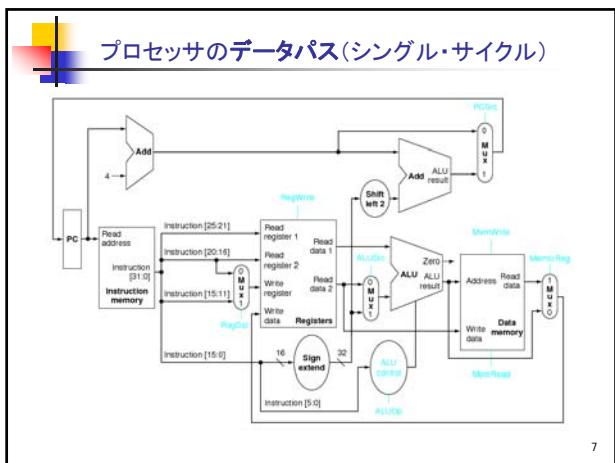

#### プロセッサのデータパス(シングル・サイクル)

op rs rt 16 bit immediate I format

0x808 lw \$t0, 4(\$s2) [ lw \$8, 4(\$18) ]

\$s2 = 0x100, MEM[0x104] = 7

2

#### Exercise

op rs rt 16 bit immediate I format

0x808 lw \$t0, 4(\$s2) [ lw \$8, 4(\$18) ]

\$s2 = 0x100, MEM[0x104] = 7

氏名, 学籍番号,

学籍番号マーク欄(右脇で)

3

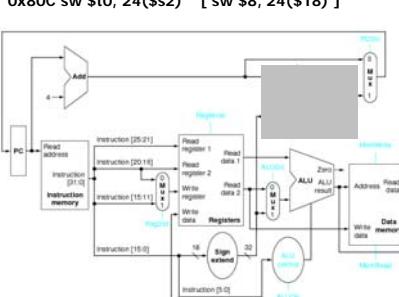

#### プロセッサのデータパス(シングル・サイクル)

op rs rt 16 bit immediate I format

0x80C sw \$t0, 24(\$s2) [ sw \$8, 24(\$18) ]

4

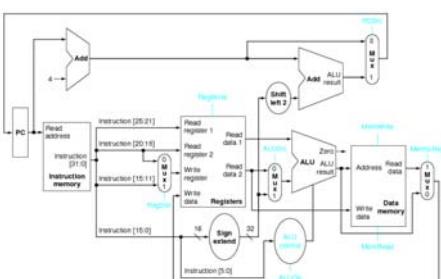

#### プロセッサのデータパス(シングル・サイクル)

op rs rt 16 bit immediate I format

0x810 beq \$s0, \$s1, Label [beq \$16, \$17, Label ]

Label: 0x80c

5

#### Exercise

op rs rt 16 bit immediate I format

0x810 beq \$s0, \$s1, Label [beq \$16, \$17, Label ]

Label: 0x80c

Ss0 = 5, \$s1 = 5

氏名, 学籍番号,

学籍番号マーク欄(右脇で)

6

7

8