# 計算機アーキテクチャ特論 (Advanced Computer Architectures)

## 4. キャッシュの実装と評価

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp www.arch.cs.titech.ac.jp

W831 講義室 木曜日 15:05 - 16:35

1

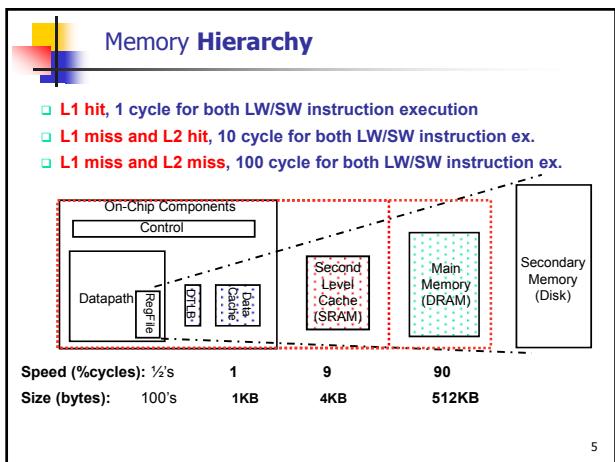

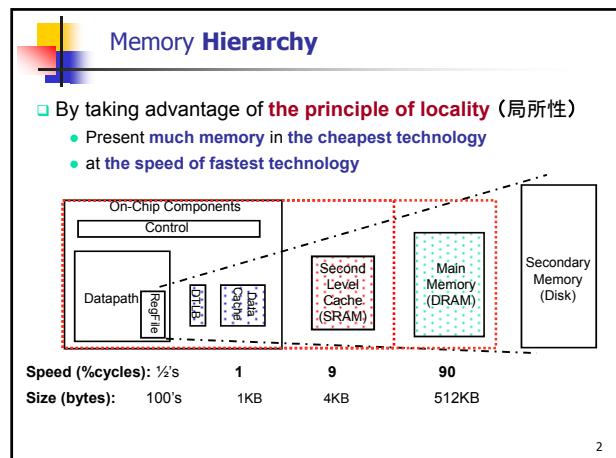

### Sample code sequence, total of 229 cycles

| Instruction | Operands       | Cycles                        |

|-------------|----------------|-------------------------------|

| lw          | \$2, \$0(\$fp) | # L1 hit, 1 cycle             |

| nop         |                | # 1 cycle                     |

| sll         | \$2,\$2,2      | # 1 cycle                     |

| move        | \$3,\$2        | # 1 cycle                     |

| lw          | \$2, \$0(\$fp) | # L1 miss, L2 miss, 100 cycle |

| nop         |                | # 1 cycle                     |

| addu        | \$2,\$3,\$2    | # 1 cycle                     |

| lw          | \$2, 0(\$2)    | # L1 miss, L2 hit, 10 cycle   |

| nop         |                | # 1 cycle                     |

| addiu       | \$2,\$2,100    | # 1 cycle                     |

| sw          | \$2, \$0(\$4)  | # L1 miss, L2 miss, 100 cycle |

| lw          | \$2, \$0(\$fp) | # L1 hit, 1 cycle             |

| sw          | \$2, \$0(\$4)  | # L1 miss, L2 hit, 10 cycle   |

6

Benchmark program test40

```

Nov 08, 12 12:23                               code.txt          Page 1/2

1 //** benchmark test40.vtl for cache evaluation 2011-11-08,Shenell KISHI */

2

3 #include <math.h>

4 #include <sys/types.h>

5 #include <sys/conf.h>

6 #include <sys/malloc.h>

7 #include <sys/param.h>

8 #include <sys/conf.h>

9 #include <sys/types.h>

10 #include <sys/malloc.h>

11 #include <sys/conf.h>

12 #include <sys/param.h>

13 #include <sys/conf.h>

14 #include <sys/param.h>

15 #include <sys/conf.h>

16 #include <sys/param.h>

17 #include <sys/conf.h>

18 #include <sys/param.h>

19 #include <sys/conf.h>

20 #include <sys/param.h>

21

22 //***** (1) memory mapped I/O

23

24 volatile int *umpoint = 0; // memory mapped I/O

25

26 //***** (2) data initialization

27

28 int a[100000], v[100000], data[100000];

29

30 //***** (3) main

31

32 for(i=0; i<100000; i++) data[i] = ELM_STID+i;

33

34 for(i=0; i<100000; i++) a[i] = 100000;

35

36 for(i=0; i<100000; i++) v[i] = 100000;

37

38 for(i=0; i<100000; i++) umpoint = a[i];

39

40 //***** (4) selection event

41

42 int l1r, l2r;

43

44 int l1 = 0;

45 int l2 = 0;

46

47 for (l1r=0; l1r<100000; l1r++) {

48     for (l2r=0; l2r<100000; l2r++) {

49         if (l1r == l2r) continue;

50

51         int tmp = a[l1r];

52         a[l1r] = a[l2r];

53         a[l2r] = tmp;

54     }

55

56     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

57

58     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

59

60     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

61

62     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

63

64     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

65

66     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

67

68     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

69

70     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

71

72     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

73

74     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

75

76     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

77

78     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

79

80     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

81

82     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

83

84     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

85

86     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

87

88     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

89

90     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

91

92     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

93

94     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

95

96     for(l1=0; l1<100000; l1++) *umpoint = a[l1];

97

98     for(l2=0; l2<100000; l2++) *umpoint = a[l2];

99

100    for(l1=0; l1<100000; l1++) *umpoint = a[l1];

101

102    for(l2=0; l2<100000; l2++) *umpoint = a[l2];

103

104    for(l1=0; l1<100000; l1++) *umpoint = a[l1];

105

106    for(l2=0; l2<100000; l2++) *umpoint = a[l2];

107

108    for(l1=0; l1<100000; l1++) *umpoint = a[l1];

109

110    for(l2=0; l2<100000; l2++) *umpoint = a[l2];

111

112}

```

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

キャラッシュに関する論文

- M.K. Qureshi, D. Thompson, Y.N. Patt.

**The V-Way Cache: Demand Based Associativity via Global Replacement.**

In Proc. of Int. Symp. Computer Architecture, ISCA 2005.

- Kaushik Rajan and R.Govindarajan.

**Emulating optimal replacement with a shepherd cache,**

In MICRO-40, pp. 445-454, 2007.

どちらか1つを選択して、プロセッサシミュレータ上に実装、性能評価する。

8

## レポート キャッシュの実装

1. SimCore/MIPS functional simulatorにキャッシュを追加して、そのヒット率とプロセッサ性能を評価する。

1. ベンチマークプログラム 40bench を用いる。

2. 命令は考慮しない LW, SW命令で参照するデータキャッシュを対象。

3. キャッシュの構成は講義スライドを参照

## レポート キャッシュの実装

### 1. 評価項目

1. ベンチマークプログラムを実行した際の、ロード命令の実行回数、ストア命令の実行回数を測定してまとめこと。メモリマップされたアドレス0へのロード、ストアはカウントしてはならない。

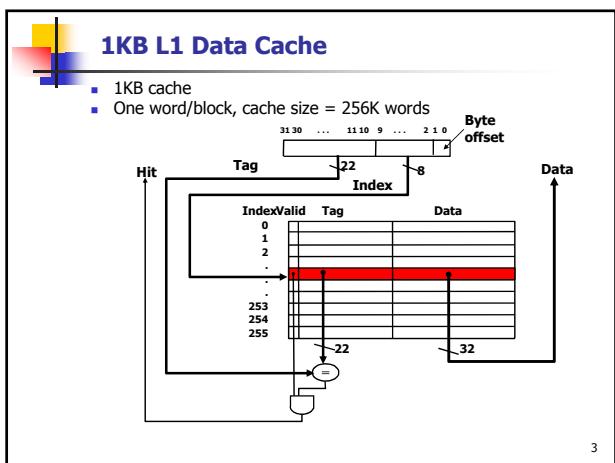

2. 1KBのL1データキャッシュを実装し、そのミス率を測定せよ。また、L1キャッシュを追加することによるプロセッサ性能の向上率を示すこと。

1. ライトアロー方式(書き込みでミスした場合も、データをキャッシュに格納)とする。

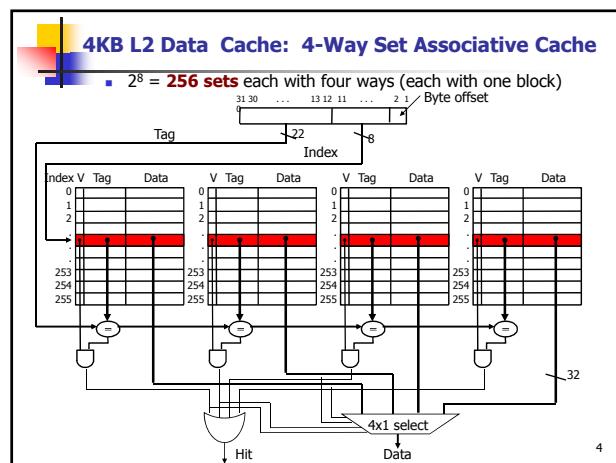

3. 4KBの標準的な4-way set associative方式のL2データキャッシュを実装し(L1データキャッシュも利用)、そのミス率を測定せよ。また、L2キャッシュを追加することによるプロセッサ性能の向上率を示すこと。

4. 講義で紹介した2つのキャッシュ方式から1つを選択し、その方式をL2キャッシュとして実装すること。ミス率を測定せよ。L2キャッシュを変更することによるプロセッサ性能の向上率を示すこと。標準的なL2より高い性能を実現すること。想定した性能が得られたか議論せよ。

## レポート 提出方法

- 12月13日の講義開始時に印刷したものを持参する。

- A4サイズで10ページ以内にまとめる。

- 実装したキャッシュのコードを掲載すること。

- 実装した各種の方式のミス率をグラフにして示すこと。

- 実装したキャッシュの挙動は本当に正しいのか、どうして正しいと主張できるか説明すること。

## 講義計画

<http://www.arch.cs.titech.ac.jp/sub5.html>

- 導入:マイクロプロセッサ

- スーパースカラプロセッサの基礎と命令レベル並列性

- **キャッシュ**

- 分岐予測

- 動的命令スケジューリングと投機処理

- メモリデータフローとデータキャッシュ

- 組込技術、低消費電力技術

- チップマルチプロセッサ

- オンチップネットワーク、メニーコアアーキテクチャ

■ 【成績評価】レポートおよび、期末レポートにより評価する。

12

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005