## 計算機アーキテクチャ 第一 (E)

### 8. メモリ2: キャッシュ

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

## Acknowledgement

- Lecture slides for Computer Organization and Design, Third Edition, courtesy of Professor Mary Jane Irwin, Penn State University

- Lecture slides for Computer Organization and Design, third edition, Chapters 1-9, courtesy of Professor Tod Amon, Southern Utah University.

2

Adapted from Computer Organization and Design, Patterson &amp; Hennessy, © 2005

### The Memory Hierarchy: Why Does it Work?

- **Temporal Locality** (時間的局所性, Locality in Time):

⇒ Keep **most recently accessed** data items closer to the processor

- **Spatial Locality** (空間的局所性, Locality in Space):

⇒ Move blocks consisting of **contiguous words** to the upper levels

3

## Cache

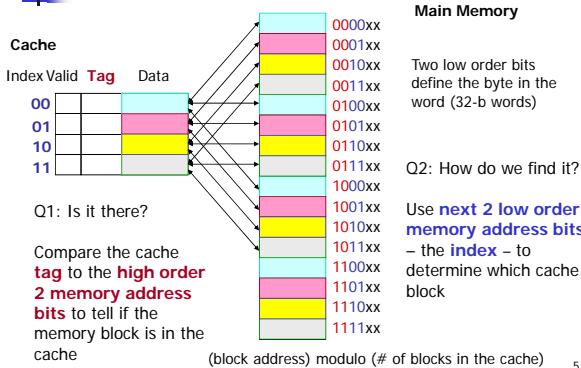

- Two questions to answer (in hardware):

- Q1: **How do we know if a data item is in the cache?**

- Q2: **If it is, how do we find it?**

- **Direct mapped**

- For each item of data at the lower level, there is exactly one location in the cache where it might be - so lots of items at the lower level must **share** locations in the upper level

- Address mapping: **(block address) modulo (# of blocks in the cache)**

- First, consider block sizes of **one word**

4

### Caching: A Simple First Example

5

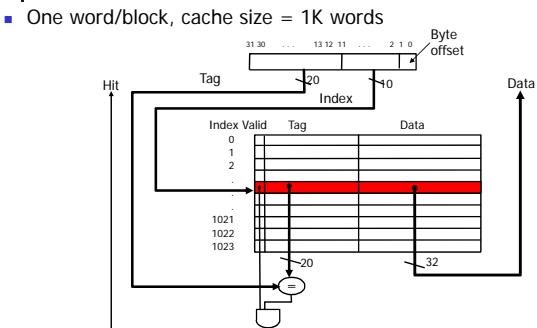

### MIPS Direct Mapped Cache Example

6

## Taking Advantage of Spatial Locality

- Let cache block hold more than one word

0 1 2 3 4 3 4 15

| 0 miss           | 1 hit             | 2 miss           |

|------------------|-------------------|------------------|

| 00 Mem(1) Mem(0) | 00 Mem(1) Mem(0)  | 00 Mem(1) Mem(0) |

|                  |                   | 00 Mem(3) Mem(2) |

| 3 hit            | 4 miss            | 3 hit            |

| 00 Mem(1) Mem(0) | 01 Mem(1) Mem(3)  | 01 Mem(5) Mem(4) |

| 00 Mem(3) Mem(2) | 00 Mem(3) Mem(2)  | 00 Mem(3) Mem(2) |

| 4 hit            | 15 miss           |                  |

| 01 Mem(5) Mem(4) | 101 Mem(5) Mem(4) |                  |

| 00 Mem(3) Mem(2) | 00 Mem(3) Mem(2)  |                  |

- 8 requests, 4 misses

13

## Handling Cache Hits (Miss is the next issue)

### Read hits (I\$ and D\$)

- this is what we want!

### Write hits (D\$ only)

- allow cache and memory to be **inconsistent**

- write the data only into the cache block (**write-back**)

- need a **dirty** bit for each data cache block to tell if it needs to be written back to memory when it is evicted

- require the cache and memory to be **consistent**

- always write the data into both the cache block and the next level in the memory hierarchy (**write-through**) so don't need a dirty bit

- writes run at the speed of the next level in the memory hierarchy – **so slow!** – or can use a **write buffer**, so only have to stall if the write buffer is full

14

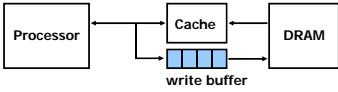

## Write Buffer for Write-Through Caching

- Write buffer** between the cache and main memory

- Processor: writes data into the cache and the write buffer

- Memory controller**: writes contents of the write buffer to memory

- The write buffer is just a **FIFO**

- Typical number of entries: 4

- Works fine if **store frequency is low**

- Memory system designer's nightmare, Write buffer **saturation** (飽和)

- One solution is to use a write-back cache; another is to use an L2 cache

15

## アナウンス

### 講義スライドおよびスケジュール

- [www.arch.cs.titech.ac.jp](http://www.arch.cs.titech.ac.jp)

- 講義日程が変更になることがあるので頻繁に確認すること。

16