## 計算機アーキテクチャ 第一 (E)

### 2. 命令形式, アドレス指定形式

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

## Acknowledgement

- Lecture slides for Computer Organization and Design, Third Edition, courtesy of **Professor Mary Jane Irwin**, Penn State University

- Lecture slides for Computer Organization and Design, third edition, Chapters 1-9, courtesy of **Professor Tod Amon**, Southern Utah University.

2

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 参考書

- コンピュータの構成と設計 第3版、バターソン & ヘネシー(成田光彰 訳)、日経BP社、2006

- コンピュータアーキテクチャ 定量的アプローチ 第4版

翔泳社、2008

- コンピュータアーキテクチャ

村岡洋一 著 近代科学社、1989

- 計算機システム工学

富田真治 村上和彰 著 昭晃堂、1988

- コンピュータハードウェア

富田真治 中島浩 著 昭晃堂、1995

- 計算機アーキテクチャ

橋本昭洋 著 昭晃堂、1995

3

## 参考書(アセンブラーに興味があれば)

MIPSのアセンブラーがよくわかります。面白いです。

MIPSとLinuxの関係がわかります。お勧め。

4

## ただししい講義の受け方？

- どんどん質問する！ >> 活発な講義！

- 難しい！

- わからない時は...

- わからない顔をする！

- 不満のある時は...

- 不満のある顔をする！

- わかった時は...

- うなずく！

5

## 計算機アーキテクチャ 第一 (E)

### 2. 命令形式, アドレス指定形式

吉瀬 謙二 計算工学専攻

kise\_at\_cs.titech.ac.jp

W641講義室 木曜日13:20 – 14:50

Aside: MIPS Register Convention

| Name        | Register Number | Usage                  | Preserve on call? |

|-------------|-----------------|------------------------|-------------------|

| \$zero      | 0               | constant 0 (hardware)  | n.a.              |

| \$at        | 1               | reserved for assembler | n.a.              |

| \$v0 - \$v1 | 2-3             | returned values        | no                |

| \$a0 - \$a3 | 4-7             | arguments              | yes               |

| \$t0 - \$t7 | 8-15            | temporaries            | no                |

| \$s0 - \$s7 | 16-23           | saved values           | yes               |

| \$t8 - \$t9 | 24-25           | temporaries            | no                |

| \$gp        | 28              | global pointer         | yes               |

| \$sp        | 29              | stack pointer          | yes               |

| \$fp        | 30              | frame pointer          | yes               |

| \$ra        | 31              | return addr (hardware) | yes               |

11

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

MIPS Arithmetic Instructions

- MIPS assembly language **arithmetic statement**

```

add $t0, $s1, $s2

sub $t0, $s1, $s2

```

- Each arithmetic instruction performs only **one** operation

- Each arithmetic instruction fits in 32 bits and specifies exactly **three** **operands**

$$\text{destination} \leftarrow \text{source1} \text{ op } \text{source2}$$

- Those operands are contained in the datapath's **register file** ( $\$t0, \$s1, \$s2$ ) – indicated by  $\$$

- Operand order is fixed (*destination first*)

12

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## MIPS Arithmetic Instructions

- MIPS assembly language **arithmetic statement**

```

add $t0, $s1, $s2

sub $t0, $s1, $s2

```

- Each arithmetic instruction performs **only one** operation

- Each arithmetic instruction fits in **32 bits** and specifies exactly **three** operands

$$\text{destination} \leftarrow \text{source1} \text{ op } \text{source2}$$

- Operand order is fixed (destination first)

- Those operands are contained in the **register file** ( $\$t0, \$s1, \$s2$ ) – **indicated by \$**

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

13

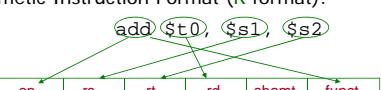

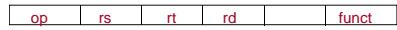

## Machine Language - Add Instruction

- Instructions, like registers and words of data, are **32 bits long**

- Arithmetic Instruction Format (**R format**):

|    |    |    |    |       |       |

|----|----|----|----|-------|-------|

| op | rs | rt | rd | shamt | funct |

|----|----|----|----|-------|-------|

- op 6-bits **opcode** that specifies the operation

- rs 5-bits register file address of the first source operand

- rt 5-bits register file address of the second source operand

- rd 5-bits register file address of the result's destination

- shamt 5-bits **shift amount** (for shift instructions)

- funct 6-bits **function code** augmenting the opcode

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

14

## MIPS Immediate Instructions

- Small constants are used often in typical code

- Possible approaches?

- put “typical constants” in memory and load them

- create hard-wired registers (like \$zero) for constants like 1

- have **special instructions** that contain constants !

- addi \$sp, \$sp, 4     # \$sp = \$sp + 4**

- slti \$t0, \$s2, 15    # \$t0 = 1 if \$s2 < 15**

- Machine format (**I format**):

|    |    |    |                  |  |

|----|----|----|------------------|--|

| op | rs | rt | 16 bit immediate |  |

|----|----|----|------------------|--|

- The constant is kept **inside** the instruction itself!

- Immediate format **limits** values to the range  $+2^{15}-1$  to  $-2^{15}$

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

15

## 演習

- $f = (g + h) - (i + j)$

- f, g, h, i, j をそれぞれレジスタ  $\$s0, \$s1, \$s2, \$s3, \$s4$  に割り付けるとする。

- 上のステートメントをコンパイルした結果のMIPSアプリケーション・コードはどうなるか。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

16

## 演習 (参考書 48ページ)

- $f = (g + h) - (i + j)$

- f, g, h, i, j をそれぞれレジスタ  $\$s0, \$s1, \$s2, \$s3, \$s4$  に割り付けるとする。

- 上のステートメントをコンパイルした結果のMIPSアプリケーション・コードはどうなるか。

```

add $t0, $s1, $s2    # $t0 = (g + h)

add $t1, $s3, $s4    #

sub $s0, $t0, $t1    #

```

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

17

## MIPS Memory Access Instructions

- MIPS has two basic **data transfer** instructions for accessing memory

```

lw $t0, 4($s3)  # load word from memory

sw $t0, 8($s3)  # store word to memory

```

- The data is loaded into (lw) or stored from (sw) a register in the register file

- The memory address – a 32 bit address – is formed by adding the contents of the **base address register** to the **offset** value

- A 16-bit field is limited to memory locations within a region of  $\pm 2^{13}$  or 8,192 words ( $\pm 2^{15}$  or 32,768 bytes) of the address in the base register

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

18

### Machine Language - Load Instruction

- Load / Store Instruction Format (I format):

$24_{10} + \$s2 =$

$$\begin{array}{r}

\dots 0001\ 1000 \\

+ \dots 1001\ 0100 \\

\hline

\dots 1010\ 1100 = 0x120040ac

\end{array}$$

Memory

|                    |           |

|--------------------|-----------|

|                    | 0xfffffff |

| 0x120040ac         | ← \$t0    |

| 0x12004094         | → \$s2    |

| 0x0000000c         |           |

| 0x00000008         |           |

| 0x00000004         |           |

| 0x00000000         |           |

| data               |           |

| word address (hex) |           |

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

19

### 演習

- $g = h + A[8]$

100語から成る配列Aがあるとする. また, コンパイラは変数g, hにレジスタ \$s1, \$s2を割り付ける. さらに配列の開始アドレスは \$s3 に納められているとする.

上のステートメントをコンパイルせよ.

20

### 演習 (参考書 50ページ)

- $g = h + A[8]$

100語から成る配列Aがあるとする. また, コンパイラは変数g, hにレジスタ \$s1, \$s2を割り付ける. さらに配列の開始アドレスは \$s3 に納められているとする.

上のステートメントをコンパイルせよ.

```

lw $t0, 32($s3)    # $t0 = A[8]

add $s1, $s2, $t0    # g = h + $t0

```

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

21

### 演習

- $A[12] = h + A[8]$

100語から成る配列Aがあるとする. また, コンパイラは変数g, hにレジスタ \$s1, \$s2を割り付ける. さらに配列の開始アドレスは \$s3 に納められているとする.

上のステートメントをコンパイルせよ.

22

### 演習 (参考書 51ページ)

- $A[12] = h + A[8]$

100語から成る配列Aがあるとする. また, コンパイラは変数g, hにレジスタ \$s1, \$s2を割り付ける. さらに配列の開始アドレスは \$s3 に納められているとする.

上のステートメントをコンパイルせよ.

```

lw $t0, 32($s3)    # $t0 = A[8]

add $t0, $s2, $t0    # $t0 = h + $t0

sw $t0, 48($s3)    # A[12] = $t0

```

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

23

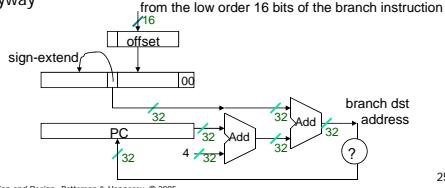

### MIPS Control Flow Instructions

- MIPS conditional branch instructions:

```

bne $s0, $s1, Lbl #go to Lbl if $s0≠$s1

beq $s0, $s1, Lbl #go to Lbl if $s0==$s1

```

- Ex:  $if (i==j) h = i + j;$

- Instruction Format (I format):

- How is the branch destination address specified?

24

## Specifying Branch Destinations

- Use a register (like in `lw` and `sw`) added to the 16-bit offset

- which register? Instruction Address Register (the **PC**)

- its use is automatically **implied** by instruction

- PC gets updated ( $PC + 4$ ) during the **fetch** cycle so that it holds the address of the next instruction

- limits the branch distance to  $-2^{15}$  to  $+2^{15}-1$  instructions from the (instruction after the) branch instruction, but most branches are local anyway

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## More Branch Instructions

- We have `beq`, `bne`, but what about other kinds of branches (e.g., branch-if-less-than)? For this, we need yet another instruction, `slt`

- Set on less than instruction:

```

slt $t0, $s0, $s1      # if $s0 < $s1      then

# $t0 = 1          else

# $t0 = 0

```

- Instruction format (**R** format):

26

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## More Branch Instructions, Con't

- Can use `slt`, `beq`, `bne`, and the fixed value of 0 in register `$zero` to **create** other conditions

- less than `blt $s1, $s2, Label`

- `slt $at, $s1, $s2 # $at set to 1 if`

- `bne $at, $zero, Label # $s1 < $s2`

- less than or equal to `ble $s1, $s2, Label`

- greater than `bgt $s1, $s2, Label`

- great than or equal to `bge $s1, $s2, Label`

- Such branches are included in the instruction set as pseudo instructions - recognized (and expanded) by the assembler

- Its why the assembler needs a reserved register (`$at`)

27

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

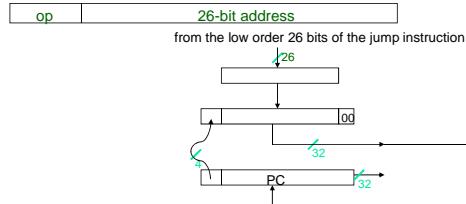

## Other Control Flow Instructions

- MIPS also has an **unconditional branch** instruction or **jump** instruction:

```

j label      #go to label

```

- Instruction Format (**J** Format):

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習 (参考書 64ページ)

- `f, g, h, i, j` は変数である。それを `$s0` から `$s4` に割り付ける。このコードをコンパイルした結果を示せ。

```

if (i == j) f = g + h; else f = g - h;

```

29

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 演習 (参考書 64ページ)

- `f, g, h, i, j` は変数である。それを `$s0` から `$s4` に割り付ける。このコードをコンパイルした結果を示せ。

```

if (i == j) f = g + h; else f = g - h;

```

```

bne $s3, $s4, Else      # if (i!=j) goto Else

add $s0, $s1, $s2      # f = g + h

j Exit                  # goto Exit

Else:

sub $s0, $s1, $s2      # f = g - h

Exit:

```

30

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

**演習**

- ループを利用して1から100までの合計値を求めるアセンブラーを示せ。

氏名、学籍番号、

学籍番号マーク欄(右詰で)

年 月 日 Arch I

31

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

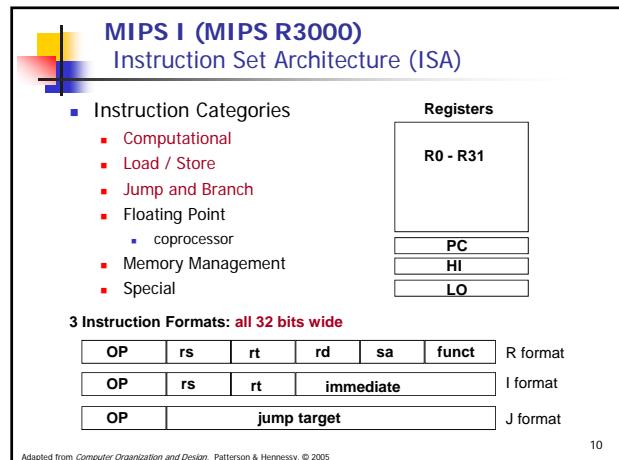

**今日のまとめ, MIPS I (MIPS R3000) ISA**

- Instruction Categories

- Computational

- Load / Store

- Jump and Branch

- Floating Point

- Memory Management

- Special

**Registers**

|          |

|----------|

| R0 - R31 |

| PC       |

| HI       |

| LO       |

3 Instruction Formats: all 32 bits wide

|    |                     |    |                   |    |       |          |

|----|---------------------|----|-------------------|----|-------|----------|

| OP | rs                  | rt | rd                | sa | funct | R format |

| OP | rs                  | rt | Immediate (16bit) |    |       | I format |

| OP | jump target (26bit) |    |                   |    |       | J format |

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

32