2010年 後学期

## 計算機アーキテクチャ 第二 (O)

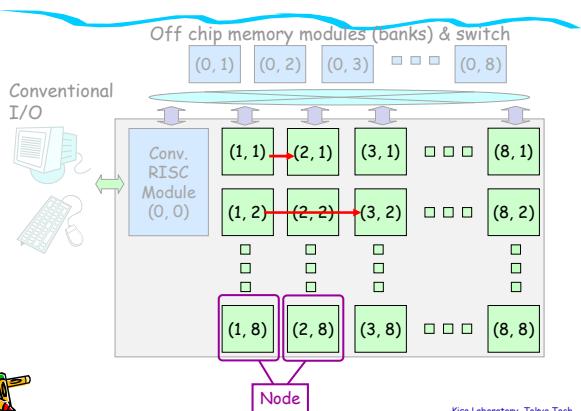

### 12. マルチコアプロセッサ, マルチコアシステム

1

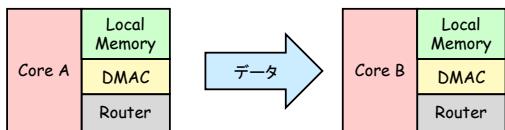

## DMA 転送 : MC\_dma\_put

- ローカルコアの保持するデータリモートコアのメモリに転送.

- 下の例は、コアAがMC\_dma\_putを呼び出し、コアBにデータを送る場合。

Kise Laboratory Tokyo Tech

7

## Library: Multi-Core library MClib

- int MC\_init(int \*id\_x, int \*id\_y, int \*rank\_x, int \*rank\_y);

- void MC\_finalize();

- void MC\_dma\_put(int dst\_id, void \*remote\_addr, void \*local\_addr, size\_t size, int remote\_stride, int local\_stride);

- void MC\_dma\_get(int get\_id, int local\_id, void \*remote\_addr, void \*local\_addr, size\_t size, int remote\_stride, int local\_stride);

- int MC\_printf(char \*format, ...);

- void MC\_puts(char\* s);

- int MC\_sprintf(char \*buf, char \*format, ...);

- int MC\_sleep(int n);

- int MC\_clock(unsigned int\*);

- etc

Kise Laboratory Tokyo Tech

8

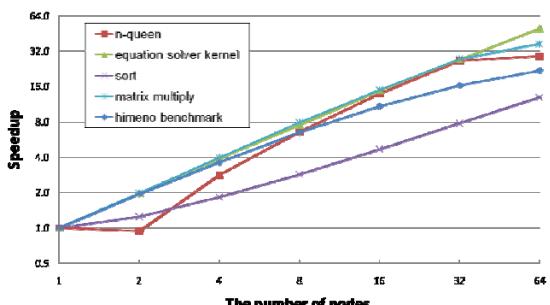

## Performance of M-Core

9

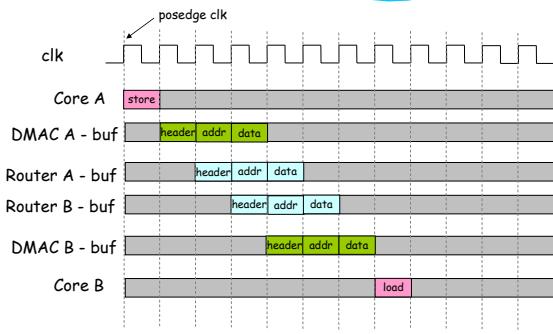

## Core to Core の通信タイミング

Kise Laboratory Tokyo Tech

10

## 通信遅延

Kise Laboratory Tokyo Tech

11

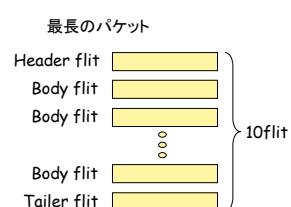

## Packet および Flit の構成

- パケット(packet)は1つの header flit, 1~9個の address, stride, data flit であり、最後のフリットは tailer のフラグを立てることによって構成される。

- パケットは最長で10flit である。

- フリット(flit)のサイズは 38ビットの固定長とする。

Kise Laboratory Tokyo Tech

12

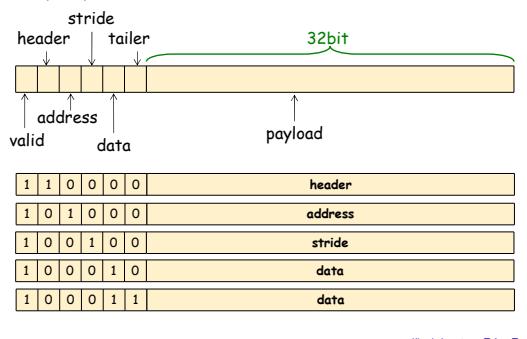

## Packet および Flit の構成

- ・ フリット(flit)は 38ビットの固定長とする

Kise Laboratory Tokyo Tech 13

レポート 提出方法

- これまでのレポートをしっかり提出している場合には、必ずしも提出する必要はありません。

- 2月14日(月)午後5時までに電子メールで提出

- report@arch.cs.titech.ac.jp

- 電子メールのタイトル

- Computer Architecture II (学籍番号)

- 電子メールの内容

- 氏名, 学籍番号

- レポート

- PDFファイルを添付

Journal of Management Education 35(7) 879-900 © 2011 Sage Publications

14

レポートA : SimMipsプロセッサシミュレータ

- **(A-1)** 004\_rand, 050\_tokei, 090\_dhry を動作させ、正しく動作していることを確認せよ。

- **(A-2)** データキャッシュのヒット率を測定する組みを追加し、ヒット率を測定せよ。

（004\_rand, 050\_tokei, 090\_dhry）

- ダイレクトマップ方式、ラインサイズは4ワードとする。

- セット数を8, 16, 32, 64, 128, 256に変更した場合のヒット率を示せ。

- このキャッシュのヒット率を改善する任意の方法を実装し、その効果を示せ。

- **(A-3)** データ値予測 (last-value predictor) の予測精度を測定する仕組みを追加し、予測精度を測定せよ。レジスタに値を書く命令が対象。

- -e40m 004\_rand.mex

- -e40m 050\_tokei.mex

- 090\_dhry

- **(A-4)** MieruPC用の面白いアプリケーションを作成せよ。その魅力を示せ。

- ソースコードは各自のディレクトリに格納すること

- MieruPC用のアプリケーションとして利用させてください。

15

Adapted from *Superscalar Microprocessor Design*, Mike Johnson

## レポートB：マルチコアプログラミング

- (B-1)** プロセッサシミュレータSimMcを利用して、与えられる行列積のプログラム(test64)を4個のコア用に並列化せよ。

4個のコアを用いて、1.5倍以上の高速化を達成すること。

ソースコード及び性能向上率を示せ。また、この課題に要した時間を示すこと。

**(B-2)** 作成したプログラムを(必要であれば)修正して、コアの数(1,2,4,8,16)と性能向上率との関係をグラフに示せ。また、この課題に要した時間を示すこと。

オリジナル・プログラムの性能を1として、グラフを描くこと。

$$\text{ans} = \mathbf{a} \times \mathbf{b}$$

Journal of Management Education 35(8) 1033-1056 © 2011 Sage Publications

16

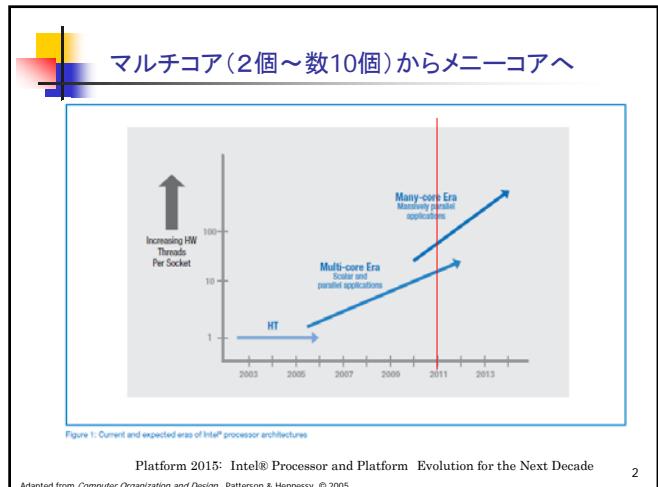

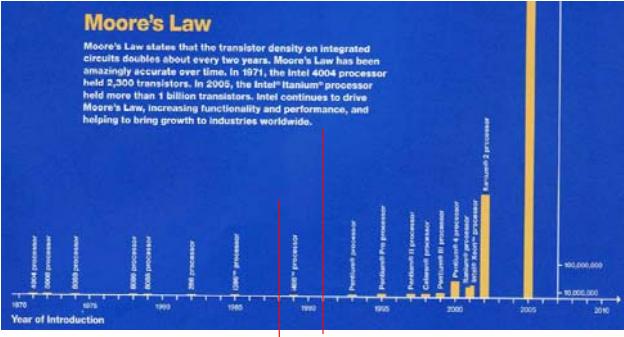

Moore's Law

Moore's Law

Moore's Law states that the transistor density on integrated circuits doubles about every two years. Moore's Law has been amazingly accurate over time. In 1971, the Intel 4004 processor held 2,300 transistors. In 2005, the Intel® Itanium® processor held more than 1 billion transistors. Intel continues to drive Moore's Law, increasing functionality and performance, and helping to bring growth to industries worldwide.

Adapted from *Superscalar Microprocessor Design*, Mike Johnson.

17

## アナウンス

- 講義スライド、講義スケジュール

- [www.arch.cs.titech.ac.jp](http://www.arch.cs.titech.ac.jp)

- 2011年2月7日 試験

- 講義用の計算機のIPアドレスが変わりました。

- ユーザ名 archo で serv.arch.cs.titech.ac.jp にログイン

- linuxなど

- ssh archo@serv.arch.cs.titech.ac.jp

- 講義時に伝えたパスワードでログイン

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

18