2009年 後学期

## 計算機アーキテクチャ 第二 (O)

### 9. アウトオブオーダ実行プロセッサ(2)

1

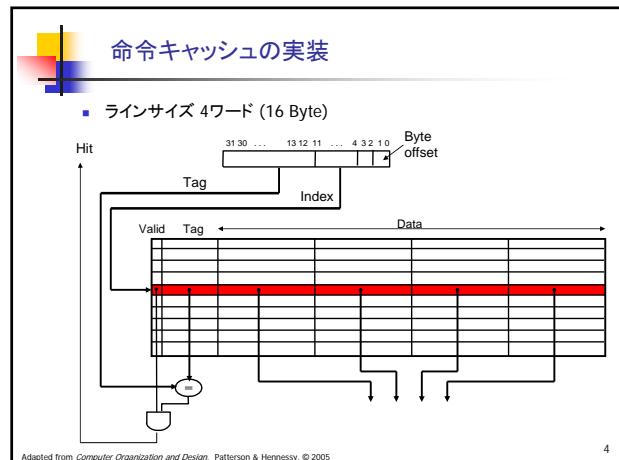

命令キャッシュの実装

```

struct icache_line {

mem = m;

data_t valid;

data_t tag;

data_t data[4];

} iline;

class lcache {

main_memory *mem;

icache_line *buf;

public:

int size;

lcache(int, main_memory*);

int fetch(data_t pc, data_t *ir);

};

class lcache {

main_memory *mem;

icache_line *buf;

public:

int size;

lcache(int, main_memory*);

int fetch(data_t pc, data_t *ir);

};

}

```

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

5

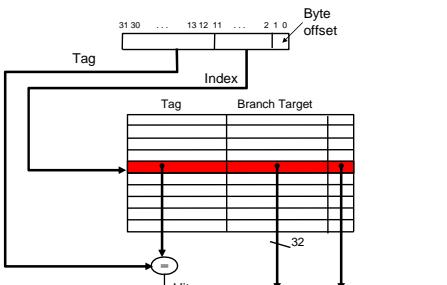

## Branch Target Buffer (BTB)の実装

```

struct btb_line {

data_t tag;

data_t data;

};

class BTB {

btb_line *buf;

public:

int size;

BTB(int);

void fetch(data_t, data_t* target);

void register(data_t, data_t);

};

BTB::BTB(int btb_size) {

size = btb_size;

buf = (btb_line *)calloc(size, sizeof(btb_line));

}

void BTB::fetch(data_t pc, data_t *target) {

int index = (pc >> 2) % size;

data_t tag = (pc >> 2);

if(buf[index].tag==tag) *target=buf[index].data;

else *target = 0;

}

void BTB::register(data_t pc, data_t target) {

int index = (pc >> 2) % size;

data_t tag = (pc >> 2);

buf[index].tag = tag;

buf[index].data = target;

}

```

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

7

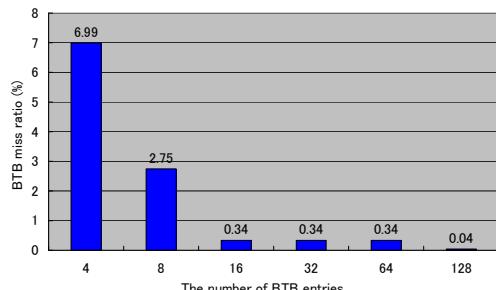

## Branch Target Buffer のミス率 (bench)

成立の分岐命令の場合のみ判定する点に注意

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

8

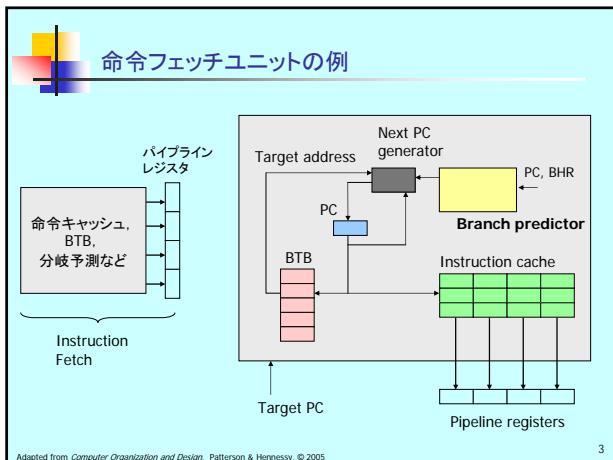

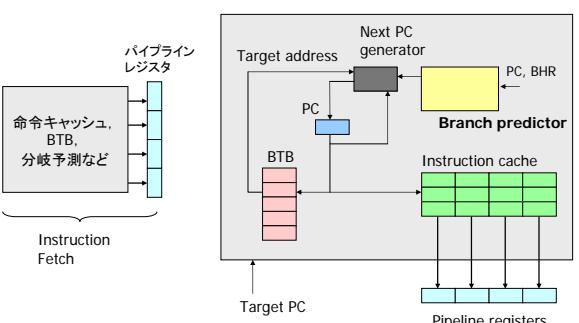

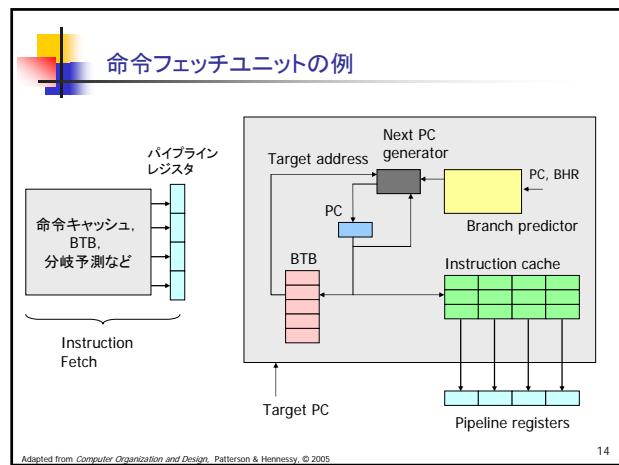

## 命令フェッчуニットの例

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## Branch Target Buffer (BTB)の改良

- キヤッシュラインに1つの分岐のみを許す

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

10

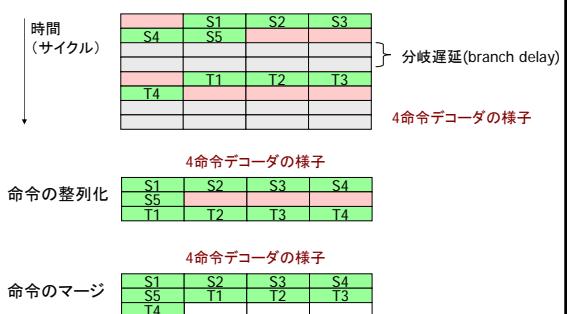

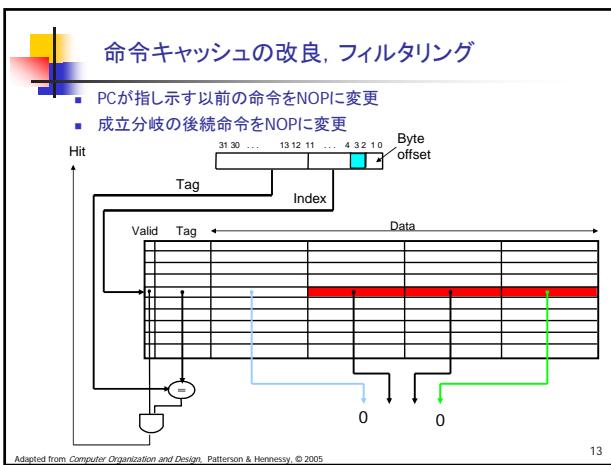

## 命令キャッシュにおけるミスマーチメント

- 分岐命令S5の飛び先をT1とする。

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

マイク・ジョンソン, スーパースカラプロセッサ

## 命令の整列化およびマージ

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

12

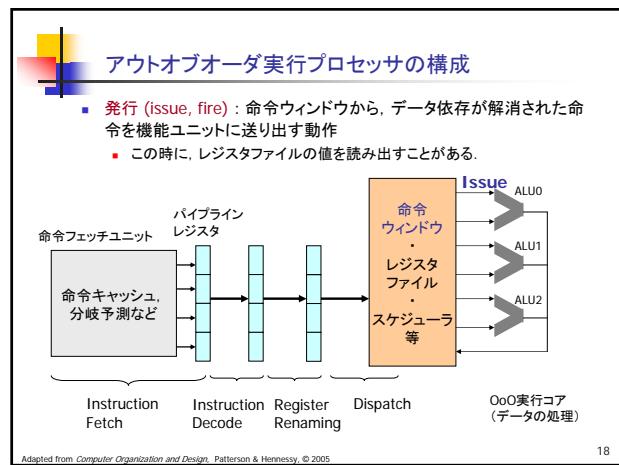

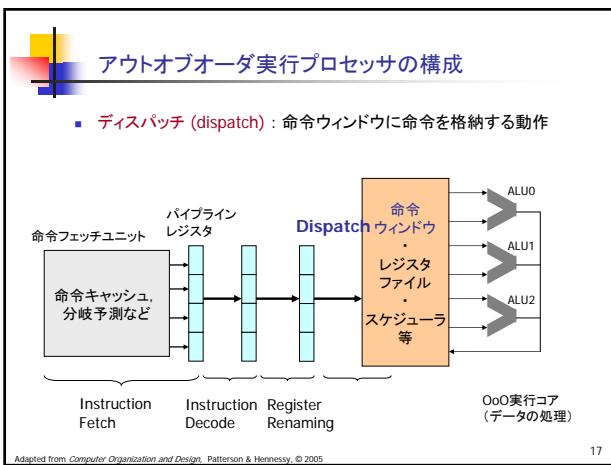

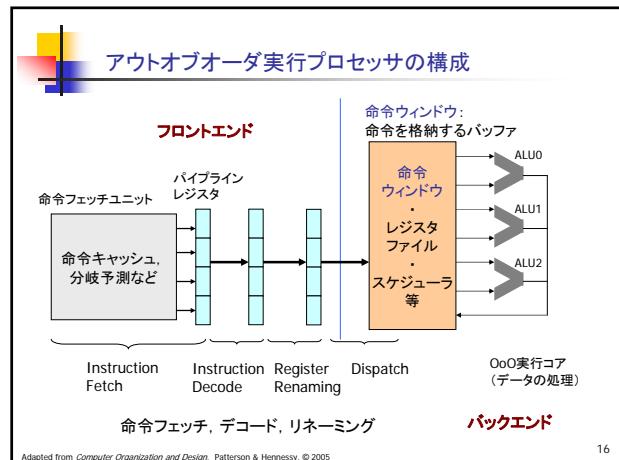

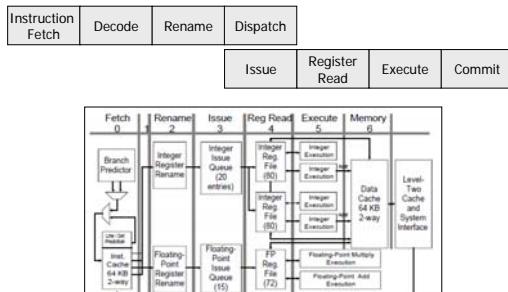

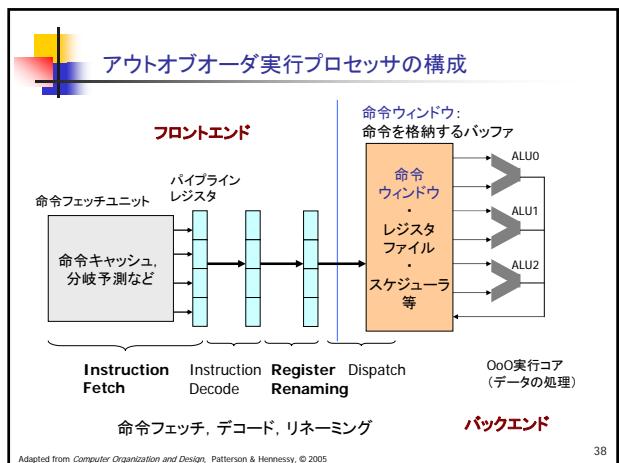

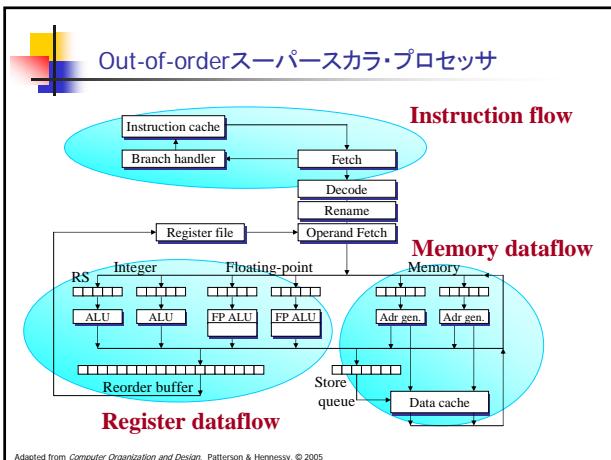

## アウトオブオーダ実行プロセッサの命令パイプライン

## 命令発行機構: Tomasuloのアプローチ

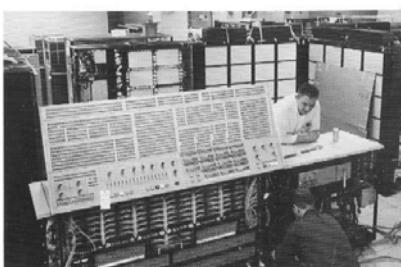

- IBM 360/91 の浮動小数点ユニットでは、アウトオブオーダ実行のための洗練された方式が採用されていた。

- Robert Tomasulo によって発明されたこの手法では

- 命令が必要とするオペランドがいつ利用できるかを探知し、RAWハザードを最小化

- レジスタリネーミングを導入してWAWハザードとWARハザードを回避

- 近年のプロセッサでは、この手法のさまざまなバリエーションが採用されているが、これら2つの重要な概念は共通の特徴

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## 命令発行機構: Tomasuloのアプローチ

- IBM 360/91 の浮動小数点ユニットでは、アウトオブオーダ実行

- Role of Tomasulo's Approach

- 浮動小数点演算の複数のオペランドを同時に発行する

- 近似値を用いてレジスタの利用を予測する

- 近似値を用いてレジスタの利用を予測する

Installation of the IBM 360/91 in the Columbia Computer Center machine room in February or March 1969. Photo: AIS archive.

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- (2)レジスタリネーミングを導入してWAWハザードとWARハザードを回避

- S と T という2つの一時レジスタが利用できると仮定

- |                                                                                                        |  |                                                                                                    |

|--------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------|

| DIV. D F0, F2, F4<br>ADD. D F6, F0, F8<br>S. D F6, 0 (R1)<br>SUB. D F8, F10, F14<br>MUL. D F6, F10, F8 |  | DIV. D F0, F2, F4<br>ADD. D S, F0, F8<br>S. D S, 0 (R1)<br>SUB. D T, F10, F14<br>MUL. D F6, F10, T |

|--------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------------------------------|

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

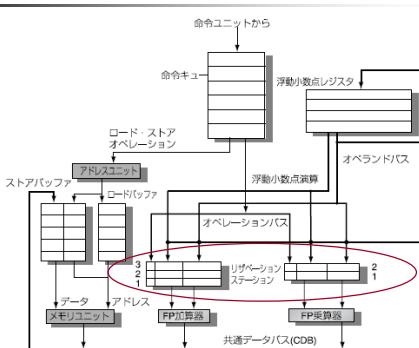

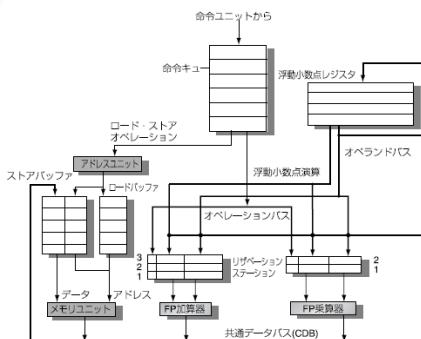

- レジスタリネーミングは発行を待つ命令のオペランドを蓄えるリザベーションステーション(命令ウィンドウの1つの実装方式)を用いて実現

- オペランドの値をリザベーションステーションに格納することで、レジスタファイルを経由しないオペランドの受け渡しを実現。

- 保留中の命令は、それらの入力を提供するリザベーションステーションを指定する。

- 複数の同じレジスタへの書き込みが生じる場合には最後のデータのみをレジスタに書き込む。

- 命令がディスパッチされる時、保留中のオペランド用のレジスタ指示子はリザベーションステーションの名前にリネームする。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- 集中化されたレジスタファイルではなく、リザベーションステーションを使用することによる2つの重要な利点

- (1)ハザード検出および実行制御の分散化

- 各機能ユニットはリザベーションステーションに保持された情報によって、そのユニットで命令がいつ実行を始めるかを決める。

- (2)実行結果がレジスタを経由するオーバヘッドを隠蔽

- 実行結果が格納されているリザベーションステーションから機能ユニットに直接渡され、レジスタを経由する必要がない。

- 実行結果は、共通の結果バスでバイパスされ、オペランドを待つユニットすべてが同時に値をロードする。

- このバスは、IBM 360/91で**共通データバス (CDB: common data bus)**と呼ばれる。

- 複数の実行ユニットを備えたパイプラインでは2つ以上のバスが必要

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- ロードバッファの3つの機能

- 計算されるまでの間、実効アドレスの要素を保持

- メモリからデータが到着するのを待っている処理中のロード命令を探知

- 完了してCDBの利用を待っているロードの結果を保持

- ストアバッファの3つの機能

- 計算されるまでの間、実効アドレスの要素を保持

- データ値がストアされるのを待っている処理中のストア命令の書き込み先メモリアドレスを保持

- メモリユニットが利用可能になるまで格納するアドレスおよび値を保持

- 浮動小数点機能ユニットとロードユニットの結果はすべてCDBを経由して、浮動小数点レジスタファイルやリザベーションステーションやストアバッファに送られる。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- 1. リザベーションステーションへの命令格納

- 命令キュー(正確なデータフローを保証するためにFIFOで命令を格納している)のヘッド(先頭)から命令を取り出す。

適切なリザベーションステーションに空きがある場合は、そこに命令を送る。

- レジスタにオペランド値がある場合は、その値も同時にリザベーションステーションに送られる。

空のリザベーションステーションがない場合、構造ハザードとなり、リザベーションステーションやバッファが解放されるまでストール。

- オペランド値がレジスタにない場合は、オペランド値を生成する機能ユニットとリザベーションステーションを検出する。

このステップがレジスタリネーミングに対応し、WARとWAWハザードを除去する。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- 2. 命令実行の開始と実行(execute)

- オペランドの1つ以上がまだ利用できない場合は、値が送られてくるのを待ちながら共通データバスを監視する。オペランドが利用可能になった時に、それを待つリザベーションステーションに格納する。すべてのオペランドが利用可能になった時に、そのオペレーションは対応する機能ユニットで実行できる。

- オペランドが利用可能になるまで命令の実行を遅らせることによって、RAWハザードを回避する。

- 同じ機能ユニットを利用する複数の命令が同一のクロックサイクルにおいて実行可能となるかもしれない点に注意する。同じクロックサイクルにおいて、個々の機能ユニットは異なる命令の実行を開始することができるが、1つの機能ユニットに対して2つ以上の命令が実行可能であれば、ユニットはそれらの中から1つを選択する。

- 整数演算、浮動小数点演算のリザベーションステーションについては、この選択は任意の方式で行うことができる。ロードとストアの場合には制約を考慮する必要がある。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- 2. 実行(execute)の続き

- ロードとストアは2段階の実行過程を必要とする。第1段階では、ベースレジスタが利用可能な場合に実効アドレスを計算する。また、得られた実効アドレスをロード・ストアバッファに格納する。

第2段階では、メモリユニットが利用可能になるとすぐに、ロードバッファのロード命令を実行する。

- ストアバッファのストア命令は、メモリユニットに送られる前に、ストアすべき値を待たなければならず。ロードとストアは実効アドレス計算を通じてプログラム順序を維持する。それによって、メモリを経由するハザードに対処できる。

- 例外の振る舞いを維持するために、命令は、プログラム順序において先行する分岐がすべて完了するまで実行を始めてはいけない。この制約により、実行中に例外を引き起こす命令が実際に実行を完了するということが保証される。

- 分岐予測を利用するプロセッサ(動的スケジューリングのすべてのプロセッサがそうであるが)では、分岐に続く命令の実行を始める前に、分岐予測が正しいことをプロセッサが知らなければならないことを意味する。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- 3. 結果書き込み(Write Result)

- 結果が利用可能になったら、CDBに結果を流し、そこからレジスタ、およびこの結果を待っているすべてのリザベーションステーション(ストアバッファを含む)に書き込む。

- ストアされる値およびストアするメモリのアドレスの両方が利用可能になると、ストア命令はストアバッファの中に保存され、メモリユニットが利用可能になるとすぐに結果が格納される。

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- リザベーションステーションが保有する7つのフィールド

- Op**: ソースオペランドS1 およびS2 に対して行うオペレーション

- Qj, Qk**: 対応するソースオペランド値を生成するリザベーションステーションの番号。値が0 の場合は、ソースオペランドがVj またはV<sub>k</sub>としてすでに利用可能であるか、不必要であることを示す。

- Vj, V<sub>k</sub>**: ソースオペランドの値。各オペランドについては、VフィールドあるいはQフィールドのどちらかが常に有効となる。ロード命令については、VKフィールドはオフセットフィールドを保持するために利用される。

- A**: ロードあるいはストア命令がメモアドレス計算の情報を保持するために利用する。最初に、命令の即値のフィールドがここに格納される。アドレス計算の後には、実効アドレスが格納される。

- Busy**: 当該リザベーションステーション、および、対応する機能ユニットが占有されていることを示す。

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

- レジスタファイルの各エントリにはQi フィールドを追加

- Qi**: その実行結果をレジスタへ格納する操作を含んでいるリザベーションステーションの番号。

- Qi の値がブランク(すなわち0)の場合は、現在、このレジスタに格納すべき結果を計算する命令が実行中でない。このため、このレジスタに格納されている内容がその値となる。

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## Tomasuloのアプローチ

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## 動的スケジューリングの例題

- 最初のロードだけが完了してその結果が書き戻されている時、次の命令列に対する状態テーブルはどのようにになっているか？

- |           |             |

|-----------|-------------|

| 1. L. D   | F6, 32 (R2) |

| 2. L. D   | F2, 44 (R3) |

| 3. MUL. D | F0, F2, F4  |

| 4. SUB. D | F8, F2, F6  |

| 5. DIV. D | F10, F0, F6 |

| 6. ADD. D | F6, F8, F2  |

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

| 命令                 | 命令状態 |    |        |  |  |  |  |

|--------------------|------|----|--------|--|--|--|--|

|                    | 発行   | 実行 | 結果書き込み |  |  |  |  |

| L. D F6, 32 (R2)   | ✓    | ✓  | ✓      |  |  |  |  |

| L. D F2, 44 (R3)   | ✓    |    | ✓      |  |  |  |  |

| MUL. D F0, F2, F4  |      | ✓  |        |  |  |  |  |

| SUB. D F8, F2, F6  |      | ✓  |        |  |  |  |  |

| DIV. D F10, F0, F6 |      | ✓  |        |  |  |  |  |

| ADD. D F6, F8, F2  |      | ✓  |        |  |  |  |  |

| 名前    | リザベーションステーション |      |                    |                |       |            |   |

|-------|---------------|------|--------------------|----------------|-------|------------|---|

|       | Busy          | Op   | Vj                 | V <sub>k</sub> | Qj    | Qk         | A |

| Load1 | no            |      |                    |                |       |            |   |

| Load2 | yes           | Load |                    |                | 44    | + Regs[R3] |   |

| Add1  | yes           | SUB  | Mem[32 + Regs[R2]] |                | Load2 |            |   |

| Add2  | yes           | ADD  |                    |                | Add1  | Load2      |   |

| Add3  | no            |      |                    |                |       |            |   |

| Mult1 | yes           | MUL  | Reg[4]             |                | Load2 |            |   |

| Mult2 | yes           | DIV  | Mem[32 + Regs[R2]] |                | Mult1 |            |   |

| フィールド | レジスタ状態 |       |    |      |      |       |     |

|-------|--------|-------|----|------|------|-------|-----|

|       | F0     | F2    | F4 | F6   | F8   | F10   | ... |

| Qi    | Mult1  | Load2 |    | Add2 | Add1 | Mult2 |     |

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

## 動的スケジューリングの例題

- 例題2.5と同じコードセグメントを利用して、MUL.D がその結果を書く準備ができている場合、状態テーブルがどのようにになっているかを示せ。

- |           |             |

|-----------|-------------|

| 1. L. D   | F6, 32 (R2) |

| 2. L. D   | F2, 44 (R3) |

| 3. MUL. D | F0, F2, F4  |

| 4. SUB. D | F8, F2, F6  |

| 5. DIV. D | F10, F0, F6 |

| 6. ADD. D | F6, F8, F2  |

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005

| 命令              | 命令状態 |    |        |

|-----------------|------|----|--------|

|                 | 発行   | 実行 | 結果書き込み |

| L.D F6,32(R2)   | ✓    | ✓  | ✓      |

| L.D F2,44(R3)   | ✓    | ✓  | ✓      |

| MUL.D F0,F2,F4  | ✓    | ✓  |        |

| SUB.D F8,F2,F6  | ✓    | ✓  | ✓      |

| DIV.D F10,F0,F6 | ✓    |    |        |

| ADD.D F6,F8,F2  | ✓    | ✓  | ✓      |

| 名前    | リザベーションステーション |      |    |                   |    |         |   |

|-------|---------------|------|----|-------------------|----|---------|---|

|       | Busy          | Op   | Vj | Vk                | Qj | Qk      | A |

| Load1 | no            |      |    |                   |    |         |   |

| Load2 | no            |      |    |                   |    |         |   |

| Add1  | no            |      |    |                   |    |         |   |

| Add2  | no            |      |    |                   |    |         |   |

| Add3  | no            |      |    |                   |    |         |   |

| Mult1 | yes           | MUL. |    | Mem[45 + Reg[R3]] |    | Reg[R4] |   |

| Mult2 | yes           | DIV  |    | Mem[34 + Reg[R2]] |    | Mult1   |   |

| レジスタ状態 |       |    |    |    |    |       |             |

|--------|-------|----|----|----|----|-------|-------------|

| フィールド  | F0    | F2 | F4 | F6 | F8 | F10   | F12 ... F30 |

| Qi     | Mult1 |    |    |    |    | Mult2 |             |

Adapted from *Computer Organization and Design*, Patterson & Hennessy, © 2005

38

40