# メディア処理で128コアを使い倒そう!

NEC メディア情報研究所 京昭倫

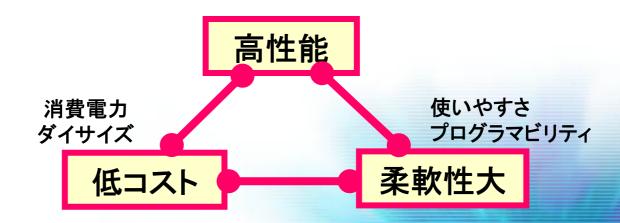

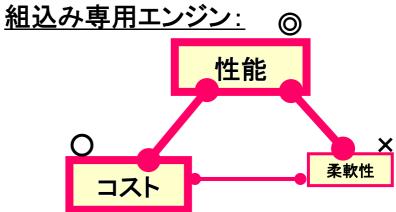

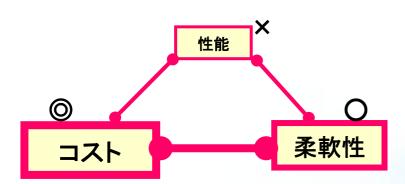

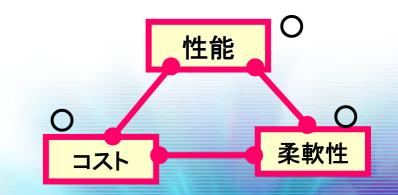

# プロセッサ設計: 二一ズは何か?

●プロセッサ設計の場合:

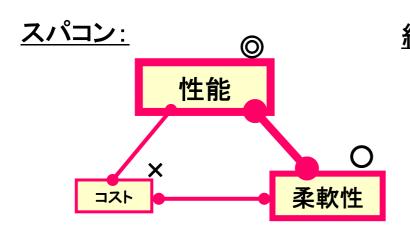

### 実際に設計・開発してみると・・・・

### マイクロコントローラ:

### <u>メディアプロセッサ:</u>

Empowered by Innovation

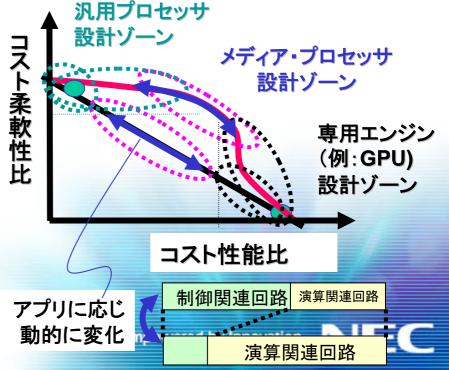

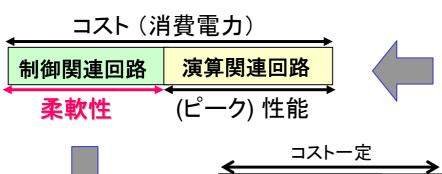

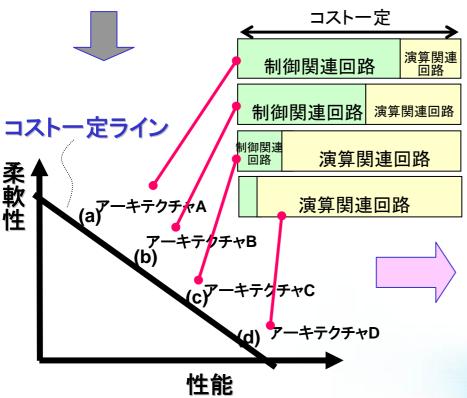

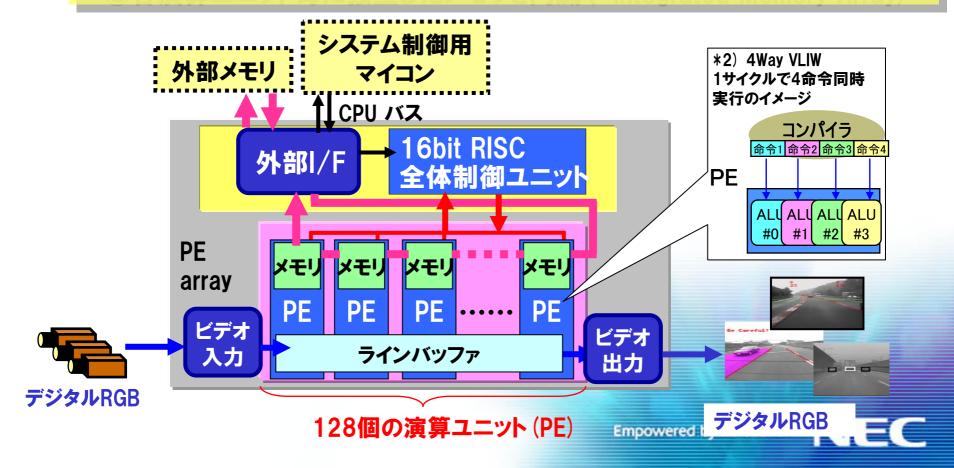

### なぜトレードオフが発生するのか?

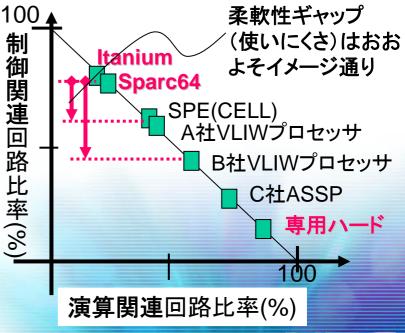

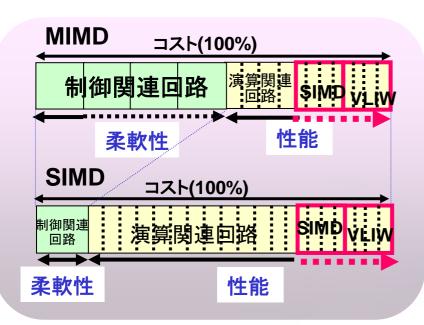

柔軟性は通常、「制御関連回路の コストにほぼ比例」と仮定すると・・

#### ダイ写真を元にプロットしてみると・・

Empowered by Innovation

NEC

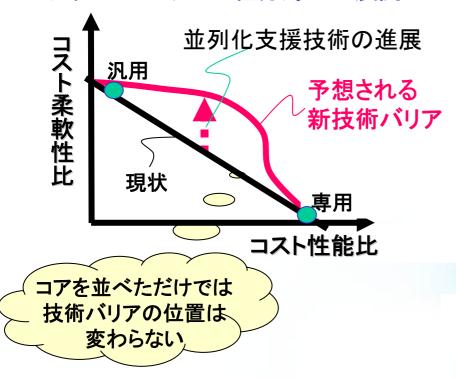

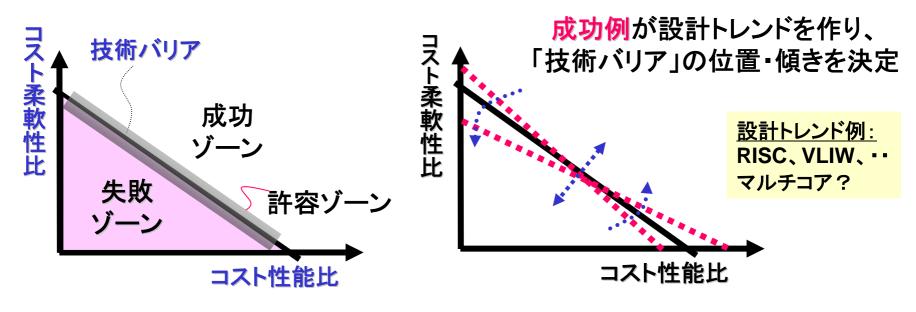

# 技術バリアの存在とその意味

技術バリアの存在を意識したプロセッサ設計が重要

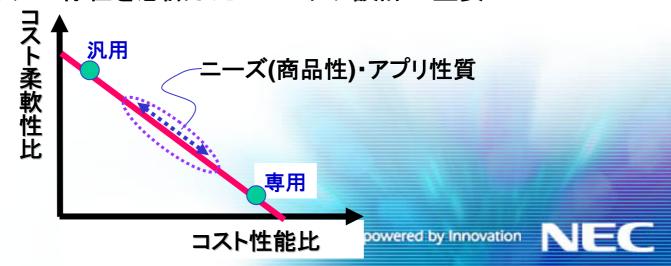

# メディア・プロセッサの場合

### アプリ性質:

膨大なデータ並列性が存在 タスク並列性も顕著 ★近年、アルゴリズムが多様化

#### 商品性(ニーズ):

| 項目  | 従来  | 近年  |

|-----|-----|-----|

| 性能  | 0   | 0   |

| コスト | 0   | O~A |

| 柔軟性 | △~× | Ο~Δ |

近年のメディア プロセッサ・設計ゾーン | NIMD+SIMD命令セット(T社:3コア.'04) | 高並列SIMD(N社:128コア.'06) | 高並列SIMD(A社:4096コア,--) | 従来の設計ゾーン: | 専用ハード+汎用高性能マイコン | 専用ハード+汎用高性能マイコン

<u>キーワード:</u>マルチコア~メニーコア(MIMD,SIMD)・VLIW・SIMD命令セット

## メディア・プロセッサのアーキテクチャ的傾向

- →多数のコアを同一命令流で制御するSIMD方式の採用例が顕著

- ⊕VLIW/SIMD命令セットの導入で、さらなるコスト性能比を狙う場合が多い

### SIMD方式採用の理由

- ・MIMDの4倍以上のコスト性能比

- ・柔軟性体感差がメディア処理では少

#### SIMDマルチコア商用例

| 名称         | PE<br>数 | PE<br>性能 | 柔軟<br>性  | 開発 元            |

|------------|---------|----------|----------|-----------------|

| Linedancer | 4096    | Δ        | Δ        | Aspec           |

| CA1024     | 1024    | Δ        | Δ        | Connex<br>Tech. |

| Xetal      | 320     | 0        | 0        | Philips         |

| IMAPCAR    | 128     | 0/       | <b>O</b> | NEC EL          |

◆コア(PE)数100~数千以上、PE単体 性能・柔軟性でバリエーション

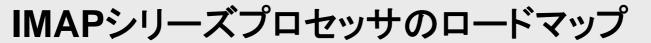

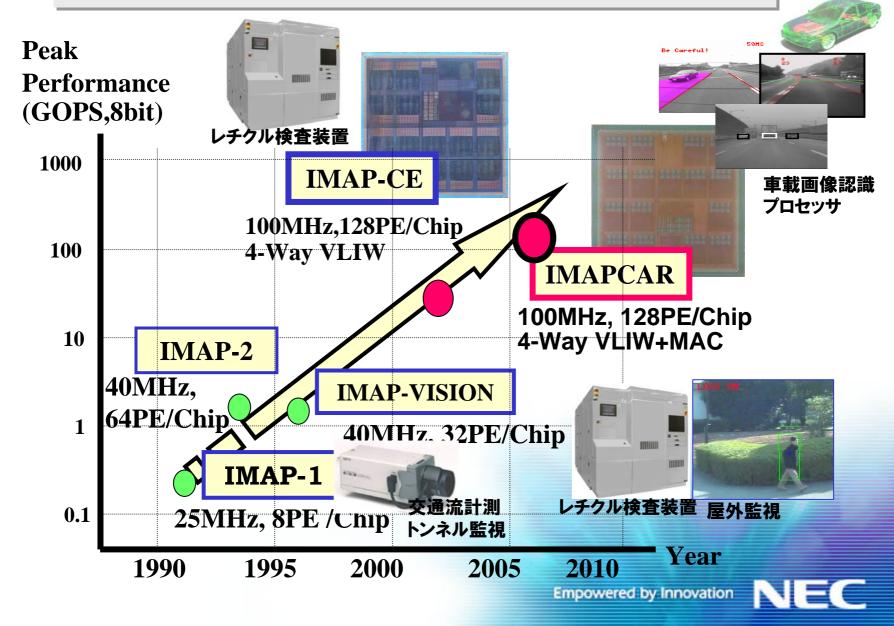

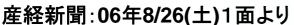

# 車載向け画像認識用並列プロセッサIMAPCAR

128個の演算ユニットの並列動作により、画像データを同時一括処理することで、リアルタイムに画像認識を実現

IMAP: Integrated Memory Array Processor

画像認識用並列プロセッサ

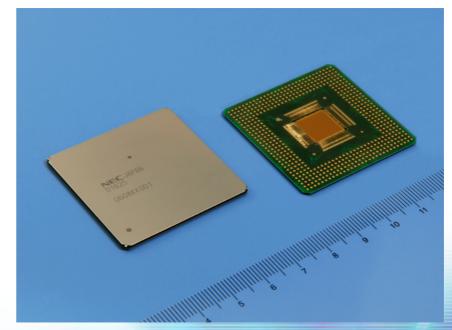

### IMAPCARブロック構成図

#### 並列処理のアーキテクチャにより大量のデータを同時一括処理可能に

- ①128の演算ユニット(PE)が同一命令に従うSIMD方式

- ②1サイクルで4命令を同時実行可能な4Way VLIW方式(\*2)

- ③各演算ユニット毎に独立したメモリを内蔵(=Integrated Memory Array)

### IMAPシリーズプロセッサでの工夫

柔軟性向上施策(使いやすくするための工夫):

- ■メモリアクセスパタンに応じた各種並列化方式を整備 ⇒PE毎に独立したメモリブロック構成(計128バンク)

- ■並列化方式の効率的実現に向けた独自のRISC型命令セット

- ■独自のデータ並列C言語・最適化コンパイラを整備

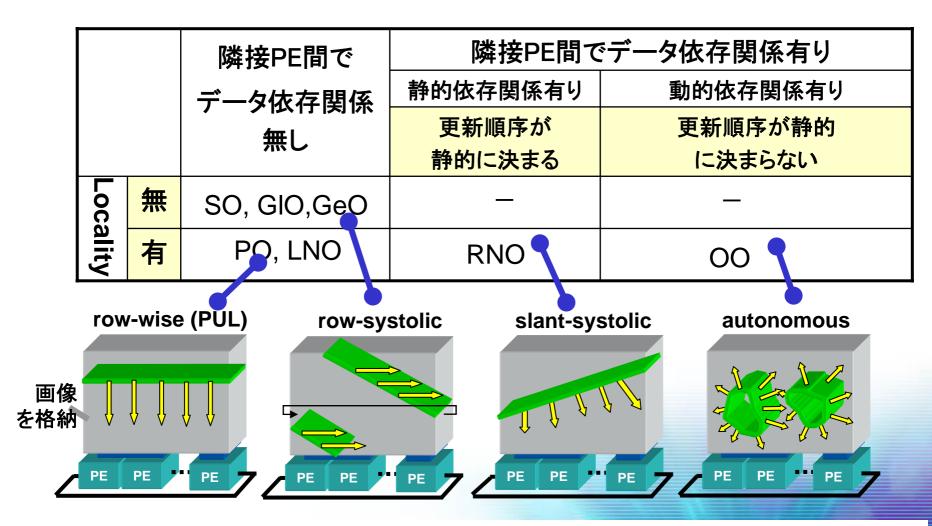

### メモリアクセスパタンに基づく並列化手法の選択

S.Kyo et.al.: "An Integrated Memory Array Processor Architecture for...", ISCA'05

S.Kyo et.al.: "An Integrated Memory Array Processor Architecture for...", to appear at IEEE Trans. Computer

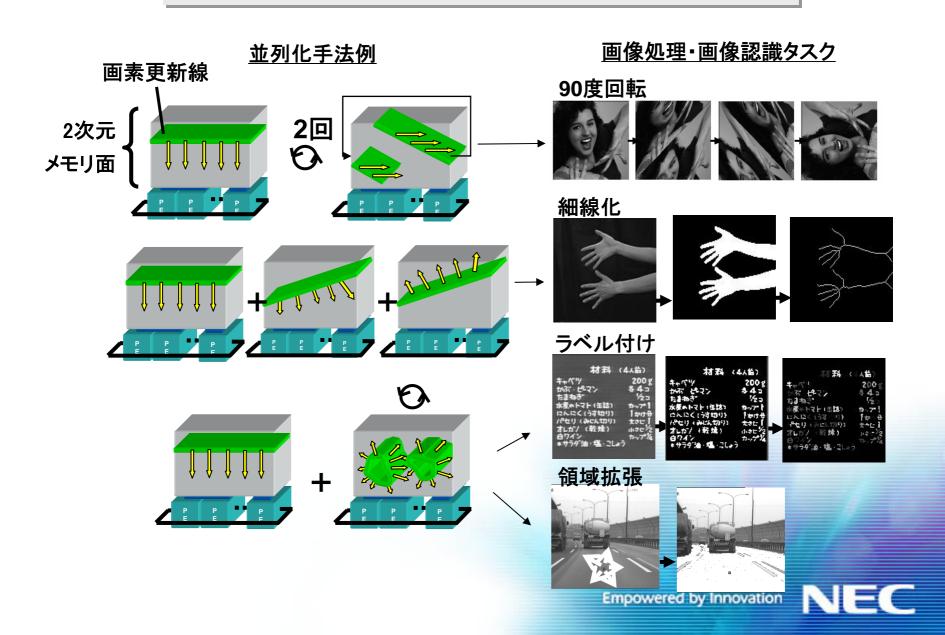

### 画像認識処理タスクの並列化例

# まとめ・技術展望

### まとめ

- @プロセッサ設計にとって避けられない技術バリアの存在

- @「Many core」構成はコスト・性能・柔軟性の良きバランスが重要な場合の一つの最適解

#### 技術展望

- ◆マルチコア向け並列化支援技術の進展に期待

- ◆「性能⇔柔軟性」を動的にトレードオフ(再構成)できれば・・・

- **キメディアプロセッサの他分野への展開**