# Workshop on Ultra Performance and Dependable Acceleration Systems (UPDAS)

held in conjunction with PDCAT'09 8<sup>th</sup>-11<sup>th</sup> Dec. 2009 @Hiroshima, Japan http://www.arch.cs.titech.ac.jp/updas/

In this workshop, we focus on hardware architecture, system software, operating system and etc. for computing systems with accelerators. As next generation computing system, we address state-of-art issues for improvement of ultra performance and dependability. And also this workshop welcomes paper submissions about practical implementations, benchmarks, and dependability related accelerators.

# **TOPICS** of particular interest include, but are not limited to:

- ✓ Accelerators for high-performance computing

- ✓ Program distribution to accelerators

- ✓ Multi/Many-core architecture for accelerating computation

- ✓ Dependable environment on accelerators

- ✓ Operating systems for accelerators

- ✓ Programming Support tools and programming models for accelerators

- ✓ Benchmarks for performance and dependability of parallel programming

- ✓ Embedded systems with accelerating architectures

- ✓ Practical implementations with accelerating architectures

- ✓ Network on Chip for accelerating architectures

## **IMPORTANT DATES**

Deadline for submission

Acceptance notification

Camera-ready

1st July, 2009

10th Aug., 2009

1st Sep., 2009

### SUBMISSION OF PAPERS

IEEE conference format, must not exceed 6 pages in length, and PDF format

Please submit your paper via updas@arch.cs.titech.ac.jp

All accepted papers will be included in conference proceedings of PDCAT'09, which will be published by IEEE Computer Society Press and automatically included in the IEEE Xplore digital library. At least one author of an accepted paper must register at the conference site and present the paper at the workshop.

### **ORGANIZING COMMITTEE**

**General Chair**

Hironori Nakajo, Tokyo University of Agriculture and Technology, Japan **Program Committee Chair**

Tsutomu Yoshinaga, The University of Electro-Communications, Japan Publication Chair

Takefumi Miyoshi, Tokyo Institute of Technology/JST, Japan Publicity Chair

Kenji Kise, Tokyo Institute of Technology, Japan

### **PROGRAM COMMITTEE**

Tsutomu Yoshinaga, The University of Electro-Communications, Japan Takefumi Miyoshi, Tokyo Institute of Technology/JST, Japan

Aaron Smith, Microsoft, USA

Atsushi Kubota, Hiroshima City University, Japan

H. Peter Hofstee, IBM, USA

Mateo Valero, Technical University of Catalonia, Spain

Naoya Maruyama, Tokyo Institute of Technology, Japan

Shinpei Kato, The University of Tokyo, Japan

Shoichi Hirasawa, The University of Electro-Communications, Japan

Takahiro Katagiri, The University of Tokyo, Japan

Takuya Araki, NEC Corp., Japan

Tor M. Aamodt, University of British Columbia, Canada

Toshinori Sato, Fukuoka University, Japan

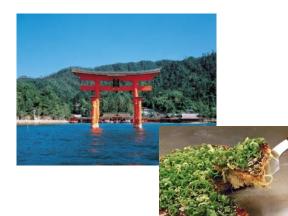

Hiroshima is good place for sightseeing, and to eat delicious food.