# SimAlpha: C++で記述したもうひとつの Alpha プロセッサシミュレータ

### 吉 瀬 謙 二<sup>†</sup> 本 多 弘 樹<sup>†</sup> 弓 場 敏 嗣<sup>†</sup>

プロセッサアーキテクチャ研究とプロセッサ教育における利用を目的として、プロセッサシミュレータ SimAlpha Version 1.0 を構築した。シンプルで理解しやすいコードであること、コードの変更が容易であることを第一の条件として C++を用いて記述した。インクルードファイルを含むコード量は約 2800 行と少ない。本稿では、実際のコードを参照しながら、SimAlpha のソフトウェアアーキテクチャを明らかにする。また、SimAlpha の利用例として SPEC CINT95 と CINT2000 の理想的な命令レベル並列性を測定した結果を報告する。

# SimAlpha: Yet Another Alpha Processor Simulator in C++

Kenji Kise,† Hiroki Honda† and Toshitsugu Yuba†

We developed a processor simulator SimAlpha Version 1.0 for research and education activities. Its design policy is to maintain the simplicity and the readability of source code. SimAlpha is written in C++ and is only 2,800 lines of code. This paper describes the software architecture of SimAlpha referring to its source code. As an actual example of use, we report the oracle IPC of SPEC CINT95 and CINT2000 benchmarks measured with SimAlpha.

#### 1. はじめに

プロセッサアーキテクチャ研究のツールとして、あるいはプロセッサ教育のツールとして様々なプロセッサシミュレータ<sup>4)</sup> が利用されている。近年の PC の高速化やクラスタの普及により、プロセッサシミュレータを動作させる環境は劇的に向上している。 その一方で、シミュレータ構築に費す時間は、実装したいアイデアの複雑化に伴い増加する傾向にある。 既存のツールをベースとして開発を進めたとしても、シミュレータの構築に数カ月を必要とする一方で、その評価は数週間で終るようなケースも珍しくない。プロセッサ研究などの目的で広く利用されているプロセッサシミュレータとして SimpleScalar Tool Set<sup>1)</sup>(以下 SimpleScalar) が有名だが、高速なシミュレーションを目的の一つとして実装されているために、必ずしも変更が容易なコードにはなっていない。

シンプルで理解しやすいコードであること、コードの変更が容易であることを第一の条件として Alpha プロセッサシミュレータ SimAlpha Version 1.0 を構築した。SimAlpha は SimpleScalar/Alpha の機能シミュレータと同等の機能をもつ。現在の実装では、命令間でオーバーラップすることなく、1 つの命令毎にプ

ロセッサの動作を模倣する。パイプライン処理やアウ トオブオーダ実行を模倣するクロックレベルのシミュ レータではないが、それらへの拡張を視野に入れた コード記述となっている。SimAlpha は SimpleScalar とは異なるポリシーで、ゼロから記述したシミュレー タである。C++を用いて記述され、インクルードファ イルを含むコード量は約2800行と少ない。SimAlpha の実装においては可読性を考慮して、グローバル変 数、goto 文、条件付きコンパイルを利用していない。 SimAlpha はSimpleScalar の置き換えを狙っているも のではなく、異なるポリシーを持つもう一つの実装を 示すことが構築の狙いである。プロセッサシミュレー タをツールとして捉えると、多くの選択肢の中から適 切なツールを選択できる利点は大きい。SimAlpha は 研究と教育のためのツールとしてのもう一つの選択肢 を提供する。

2章では SimAlpha の動作環境と検証手法を、3章では実際のコードを参照しながらソフトウェアアーキテクチャを明らかにする。4章では SimAlpha の利用例として理想的な並列性を測定した結果を示し、5章で本稿をまとめる。

## 2. SimAlpha の実行と動作検証

SimAlpha は Intel アーキテクチャ上の Linux 環境で動作する。レジスタの内容とメモリの内容を列挙した SimAlpha 独自の実行イメージを与えることでシ

Graduate School of Information Systems, The University of Electro-Communications

<sup>†</sup> 電気通信大学 大学院情報システム学研究科

ミュレーションを開始する。ELF や COFF といった 実行ファイル形式の知識が不要であり、複雑なローダ を SimAlpha の実装から切り離すことができるという 利点から、図 1 に示す独自形式の実行イメージファイ ルを採用した。実行イメージファイルは Alpha バイ ナリから構成できる 。

```

/* SimAlpha 1.0 Image File */

/*** Registers ***/

/@reg 16 0000000000000003

/@reg 17 00000011ff97008

/@reg 29 0000000140023e90

/@reg 30 000000011ff97000

/@pc 32 0000000120007d80

/*** Memory ***/

@11ff97000 00000003

@11ff97008 1ff97138

@11ff9700c 00000001

```

図 1 SimAlpha の実行イメージファイル

Pentium III 1GHz、メインメモリ 512MB の計算機上で SPEC CINT95 と CINT2000 の 20 本のプログラムを用いて SimAlpha と sim-safe<sup>1)</sup> の動作速度を測定したところ、sim-safe のシミュレーション速度 3.1 MIPS に対して、SimAlpha のシミュレーション速度は 1.1 MIPS という結果となった。SimAlpha のコンパイルには egcs-1.1.2 release、最適化オプション O2 を用いた。SimpleScalar と比較して、約 3 倍のシミュレーション時間が必要となる点が SimAlpha の欠点の一つとなっている。ただし、シミュレータ開発の時間が支配的な場合にその開発時間を短縮できるとすれば、シミュレーション速度で 3 倍の速度差は問題にならない範囲といえる。

SimAlphaは、アーキテクチャステートの動作レベルで、SimpleScalar との互換性を確認している。SPEC CINT95 と CINT2000 の 20 個のベンチマークプログラムを利用して、1 つの命令を実行する度に、SimAlphaのアーキテクチャステート(プログラムカウンタ、32 本の整数レジスタ、32 本の浮動小数点レジスタ)と、SimpleScalar のアーキテクチャステートの全ての値を比較し、一致することを確認している。 従来のシミュレータでは、グローバル変数の存在などにより、一つのプロセス内に 2 つのシミュレーションのイメージを作ることは難しかった。このため、正しい実行結果をトレースとしてファイルに保存し、これと比

SimAlpha の実行イメージファイルは SimpleScalar のローダ を利用して作成できる。また、ハンドアセンブル等により命令 列を作成してステップ実行することで、短い命令列の挙動を容易に把握できる。

2 つのシミュレータのアーキテクチャステートの値を一致させ るために、SimAlpha の動作を、SimpleScalar の望ましくな い挙動と一致させた箇所が 3 つ存在する。また、一部のシステ ムコールの実装において SimpleScalar のコードを変更した。 較することで、もうひとつのシミュレータの検証をおこなっていた。SimAlpha の場合には、高速かつ確実に検証をおこなう手段として、SimpleScalar などのプログラムに SimAlpha のオブジェクトを埋め込む機能を提供する。これを実現するために、C のインターフェースを提供するとともに、ファイル識別子の値を厳密に一致させるための工夫を凝らしている。検証のために必要となる SimpleScalar のコード変更は 1ヶ所で約 40 行と非常に少ない。

SimAlphaの提供する、複数のシミュレーションイメージを作成したり、あるシミュレータの中にオブジェクトを埋め込んで検証する手法は、SimAlphaとSimpleScalarの間の検証に利用されるだけではなく、開発中の幾つかのシミュレータの動作を検証するためにも利用することができる。この機能を利用することで、開発中のシミュレータのバグを早期に発見したり、シミュレータの正当性を確認することが可能になる。

#### 3. ソフトウェアアーキテクチャ

本章では、SimAlphaのコードの高い可読性を示すために、変更を加えていないC++の本物のコード (疑似コードではない)を示しながら、SimAlphaの実装内部の説明を試みる。まず、メイン関数の説明から始め、そこで生成されるオブジェクト chip のコンストラクダが、更に7つのオブジェクトを生成することを見る。それらオブジェクト間の関係を見た後に、重要な役割を果たすクラス instruction の定義とコードを説明する。

```

int main(int argc, char **argv){

if(argc==1) usage();

char *p = argv[argc-1]; /* program name */

char **opt = argv; /* options */

simple_chip *chip = new simple_chip(p, opt);

while(chip->step());

delete chip;

return 0;

}

```

図 2 SimAlpha のメイン関数

図 2 に示すメイン関数では simple\_chip 型のオブジェクト chip を生成する。1 つの命令を実行するメンバ関数 step は、実行する命令がなくなった時点 (アプリケーションのシミュレーションが終了した時点) で値 0 を返す。while ループにより、関数 step が値 0 を返すまで繰り返すことでシミュレーションを進めていく。実行が終わるとオブジェクト chip を解放し、その際に呼ばれるデストラクタがシミュレーション結果を表示する。

クラス simple\_chip のコンストラクタを図3に示す。

```

simple_chip::simple_chip(char *prog, char **opt){

sc = new system_config(prog, opt);

e = new evaluation_result;

as = new architecture_state(sc, e);

mem = new memory_system(sc, e);

deb = new debug(as, mem, sc, e);

sys = new system_manager(as, mem, sc, e);

p = new instruction(as, mem, sys, sc, e);

}

```

図 3 simple\_chip のコンストラクタ

```

instruction p

system_manager sys

architecture_state as memory_system mem

system_config sc evaluation_result e

```

図 4 simple\_chip で作られる 6 つのオブジェクトの参照関係

図 5 アーキテクチャステートの定義

simple\_chip 型のオブジェクトの生成時に、7種類のオ ブジェクトが生成される。デバッグのために利用する deb を省略した 6 つのオブジェクトの参照関係を図 4 に示す。system\_config 型のオブジェクト sc には、シ ミュレーションの対象となるシステム設定の情報など を格納する。これらの値はシミュレーションの開始前 に定義され、原則として、シミュレーション中に値が変 わることはない。evaluation\_result 型のオブジェクト e には評価中のデータを保存する。変数の値はシミュ レーションの実行中に更新されるが、これらの値がシ ミュレーションの実行に影響を与えることはない。オ ブジェクト sc と e は、その他の全てのオブジェクトか ら参照される。プログラムカウンタ、整数レジスタ、浮 動小数点レジスタから成るクラス architecture\_state の定義を図 5 に示す。architecture\_state 型のオブジェ クト as と、ロードストア命令などにより参照される メモリシステムを実現する memory\_system 型のオブ ジェクト mem がシミュレーション実行における計算 結果などの状態を保持する。これら2つのオブジェク トは、instruction 型のオブジェクト p と、システム コールなどを処理する system\_manager 型のオブジェ クト sys によって更新される。本稿ではオブジェクト sys の説明は省略する。

ステップ実行をおこなうクラス simple\_chip のメン

```

int simple_chip::step(){

p->Fetch(&as->pc);

/* pipeline stage 0 */

p->Slot();

/* pipeline stage 1 */

p->Rename();

/* pipeline stage 2 */

p->Issue();

/* pipeline stage 3 */

p->RegisterRead();

/* pipeline stage 4 */

p->Execute(&as->pc);

/* pipeline stage 5 */

p->Memory();

/* pipeline stage 6 */

p->WriteBack();

/* split a conditional move, see README.txt */

execute_cmovb(p, as);

e->retired_inst++;

house_keeper(sys, sc, e, deb);

return sys->running;

```

図 6 関数 step のコード

バ関数 step のコードを図 6 に示す。instruction 型のオブジェクト p に対して、パイプラインステージに対応する 7 つの関数と WriteBack の 8 つの関数を順番に呼び出すことで 1 つの命令を実行する。SimAlpha Version 1.0 では機能レベルシミュレータの能力しか提供しないが、コードの可読性と拡張性を考慮して、Alpha21264<sup>3)</sup> の命令パイプラインを参考にしながら命令の動作を 8 つのステージに分割して記述した。以降、クラス instruction の定義と、8 つのステージに対応する関数のコードを説明する。ただし、関数 Rename では処理をおこなっていないので、この関数の説明は省略する。

クラス instruction の定義を図 8 に示す。パイプラインステージに対応する関数が呼びだされ、命令の処理が進むに従って、オブジェクト内のプライベート変数の値が計算されていく。

```

int instruction::Fetch(data_t *pc){

mem->ld_inst(pc, &ir);

Npc.init(pc->ld() + 4);

return 0;

}

```

図7 命令フェッチステージのコード

命令フェッチステージのコードを図 7 に示す。プログラムカウンタ PC の示すアドレスから 4 バイトの命令をロードして、変数 ir に格納する。また、PC に値 4 を加えて得られる次命令のアドレスを Npc に格納する。

スロットステージのコードを図 9 示す。先のステージでフェッチした命令コード ir を用いて、幾つかの変数の値をデコードする。図 9 の様にデコードした値を変数に代入する替わりに、マクロを用いてコードを記述することができる。後者の方法を用いることで、シミュレーション時間の向上を期待できるが、コードの

```

int instruction::Slot(){

class instruction{

Op = (ir>>26) \& 0x3F;

evaluation_result *e;

RA = (ir>>21) & 0x1F;

architecture_state *as;

RB = (ir>>16) \& 0x1F;

system_manager

RC = (ir)

) & 0x1F;

memory_system

*mem:

WF = ((0p\&MSK2)==0x14 \mid | (0p\&MSK2)==0x20);

INST_TYPE ir; /* 32bit instruction code */

LA = (0p==0x08 | | 0p==0x09);

LD = (Op==0x0a | | Op==0x0b | | Op==0x0c | |

/* Opcode field

*/

(0p\&MSK2)==0x20 || (0p\&MSK2)==0x28);

/* Ra field of the inst

int RA:

ST = (Op==0x0d | | Op==0x0e | | Op==0x0f | |

int RB:

/* Rb field of the inst

*/

int RC;

/* Rc field of the inst

*/

(0p\&MSK2) == 0x24 \mid \mid (0p\&MSK2) == 0x2c);

int ST;

/* store inst ?

*/

BR = ((0p\&MSK4)==0x30);

WB = (LD || (0p\&MSK2)==0x08 || 0p==0x1a ||

/* load inst ?

int LD;

*/

/* load address inst ?

0p==0x30 \mid | 0p==0x34) ? RA :

int LA:

*/

((Op\&MSK3)==0x10 \mid | Op==0x1c) ? RC : 31;

int BR;

/* branch inst ?

*/

/* Rav is immediate ?

Af = (0p==0x15 \mid | 0p==0x16 \mid | 0p==0x17 \mid |

int Ai;

Op==0x1c ||

int Bi;

/* Rbv is immediate ?

*/

(0p\&MSK2) == 0x24 || (0p\&MSK3) == 0x30);

int Af:

/* Rav from floating-reg ? */

Bf = ((0p\&MSK2)==0x14);

int Bf;

/* Rbv from floating-reg ? */

int WF;

/* Write to the f-reg ?

Ai = (0p==0x08 \mid | 0p==0x09 \mid | LD);

*/

Bi = (BR || (Op&MSK2)==0x10 && (ir & BIT12));

int WB;

/* Writeback reg index

*/

data_t Npc; /* Update PC or PC + 4

*/

data t Imm: /* immediate

/** For the CMOV Split Code (CMOV1) **/

*/

data_t Adr; /* load & store address

if(cmov_ir_create(ir)){

RB = RC:

data_t Rav; /* Ra

data_t Rbv; /* Rb

*/

Bi = 0;

data_t Rcv; /* Rc

return 0;

public:

}

int Fetch(data_t *);

int Fetch(data_t *, INST_TYPE);

図 9 スロットステージのコード

int Slot():

int Rename();

int instruction::Issue(){

int Issue();

DATA_TYPE Lit, D16, D21, tmp, d21e, d16e;

int RegisterRead();

d21e = ((ir & MASK21) | EXTND21) << 2;

int Execute(data_t *);

d16e = (ir & MASK16) | EXTND16;

int Memory();

int WriteBack();

Lit = (ir>>13) & 0xFF;

D21 = (ir & BIT20) ? d21e : (ir&MASK21)<<2;

INST_TYPE get_ir();

D16 = (ir & BIT15) ? d16e : (ir&MASK16);

int data_ld(data_t *, data_t *);

if(0p==0x09) D16 = (D16 << 16);

int data_st(data_t *, data_t *);

instruction(architecture_state *,

tmp = (LA||LD||ST) ? D16 : (BR) ? D21 : Lit;

memory_system *,

Imm.init(tmp);

system_manager *,

return 0;

system_config *,

evaluation_result *);

図 10 発行ステージのコード

};

図 8 クラス instruction の定義

```

可読性を考慮して変数に代入する方法を選択した。また、このような記述方法は Verilog-HDL の記述と近く、C++と Verilog-HDL との間の部分的なコードの再利用を可能とする。

発行ステージのコードを図 10 示す。ここでは、命令の種類に応じて必要となるイミディエート Imm のデータを作成する。これらのデータや、アーキテクチャステート、メモリの内容は図 15 に示す data\_t 型のオブジェクトとして定義されている。

レジスタリードステージのコードを図 11 を示す。

```

浮動小数点レジスタあるいは整数レジスタからデータ

を読みだし、Rav と Rbv に格納する。

```

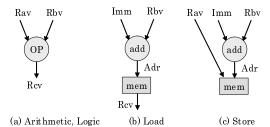

実行ステージのコードを図 12 に示す。実行ステージでは、3 つのデータを更新する。算術命令等は Ravと Rbv を入力として Rcv の値を計算する。ロードストア命令はメモリ参照アドレス Adr を計算する。分岐命令は分岐先アドレス Tpc を計算する。

メモリアクセスステージのコードを図 13 に示す。ストア命令の場合には Rav の値をメモリにストアする。ロード命令の場合にはロードした値を Rev に保存する。

```

int instruction::RegisterRead(){

Rav = Ai ? Imm : Af ? as -> f[RA] : as -> r[RA];

Rbv = Bi ? Imm : Bf ? as \rightarrow f[RB] : as \rightarrow r[RB];

}

図 11 レジスタリードステージのコード

int instruction::Execute(data_t *Tpc){

/*** Update Rcv ***/

if(BR || Op==OP_JSR){

Rcv=Npc;

}

else if(!LD){

ALU(ir, &Rav, &Rbv, &Rcv);

/*** Update Adr ***/

Adr.init(0):

if(LD || ST){

ALU(ir, &Imm, &Rbv, &Adr);

/*** Update Tpc ***/

*Tpc = Npc;

if(Op==OP_JSR){

*Tpc = Rbv;

Tpc->st(Tpc->ld() & ~3ull);

if(BR){

BRU(ir, &Rav, &Rbv, &Npc, Tpc);

}

return 0;

}

図 12 実行ステージのコード

int instruction::Memory(){

if(ST) data_st(&Adr, &Rav);

if(LD) data_ld(&Adr, &Rcv);

return 0;

図 13 メモリアクセスステージのコード

int instruction::WriteBack(){

if(Op==OP_PAL){

sys->execute_pal(this);

if(!WF && WB!=31) as->r[WB] = Rcv;

if( WF && WB!=31) as->f[WB] = Rcv;

return 0;

図 14 ライトバックのコード

```

ライトバックのコードを図 14 示す。実行している 命令が PAL コードである場合には、execute\_pal 関 数を呼びだす。結果を生成する通常の命令の場合は、 データ Rcv をレジスタファイルに格納して当該命令 の実行を完了する。

## 4. SimAlpha の利用例

本章では、SimAlpha の拡張性を示す例として、制御依存関係や資源競合を解消し、データ依存関係のみを制約として得られる理想的な命令レベル並列性を測定するように SimAlpha を拡張する。また、これを用いて測定した結果を報告する。測定する値は文献 2)の oracle IPC と同様の意味を持つ。ベンチマークには SPEC CINT95 と CINT2000 を利用した。

SimAlpha で扱うデータは、単なる unsigned long long 型の値ではなく、data\_t 型のオブジェクトとして定義される。理想的な命令レベル並列性を測定するために、計算された全てのデータにデータフローグラフの高さに相当する値 (これをランクと呼ぶことにする)を格納するようにクラス data\_t を変更する。物理メモリはクラス data\_t のオブジェクトの配列として構築されている。ロードストア命令は1バイトから8バイトの粒度でメモリを参照するので、メモリ内のデータをオブジェクトとして表現する際の粒度には幾つかの選択肢があるが、8バイト単位の整列したデータを一つのオブジェクトとした。理想的な命令レベル並列性を測定するために変更されたクラス data\_t の定義を図 15 に示す。

```

class data_t{

uint64_t value;

public:

int cmov;

uint32_t rank; /* This line is inserted. */

uint64_t ld();

int st(uint64_t);

int init(uint64_t);

};

```

図 15 データオブジェクト data\_t の定義

ランクの計算方法を図 16 に示す。算術論理命令は、ALU によりデータが計算される時に、2 つの入力オペランド Rav と Rbv のランクの最大値に演算レイテンシを加えた値を計算結果 Rev のランクとして格納する。ロード命令では、Rbv のランクにアドレス計算のためのレイテンシとメモリ参照レイテンシを加えることでランクを計算する。ストア命令は、メモリに書き込むデータ Rav と、アドレス計算により得られるランクとの最大値をデータのランクとしてメモリに格納する。

シミュレーション中には、個々のデータが持つランクとは別に、全データのランクの最大値を更新する。シミュレーションが終了した時点のランクの最大値がデータフローグラフの高さを表すので、この値と実行命令数から理想的な並列性を計算できる。ただし、データはシステムコールを越えてスケジューリングで

- (a) rank(Rcv) = max(rank(Rav), rank(Rbv)) + latency(OP)

- (b)  $\operatorname{rank}(\operatorname{Rev}) = \operatorname{rank}(\operatorname{Rbv}) + \operatorname{latency}(\operatorname{add}) + \operatorname{latency}(\operatorname{mem})$

- (c) rank = max(rank(Rav), rank(Rbv) + latency(add))

図 16 命令タイプ毎のランクの計算方法

きないという制約を加えた。以下の評価において、ランクを計算する際の演算レイテンシとメモリ参照レイテンシを1サイクルとした。CINT2000の9つのベンチマークに関しては University of Minnesota が提供している縮小入力セットを利用した。それ以外のベンチマークにおいては、シミュレーションの命令数を抑えるように入力パラメタを調整した。SPEC CINT95のバイナリは DEC C コンパイラ、最適化オプションO4を用いて生成した。SPEC CINT2000のバイナリは、SimpleScalar のサイトからダウンロードしたものを利用した。

理想的な並列性を測定するために SimAlpha に変更を加えた。この変更の多くの部分はデータが生成される際のランクの計算であり、追加した全てのコードはわずか 26 行だった。変更点の詳細は省略するが、変更前後のソースコードは本稿の最後に示す URL からダウンロードできる。

測定結果を表 1 に示す。変更後のクラス data\_t の定義に示した様に、ランクを保持するための変数の追加によりシミュレーションのためのメモリ量が増加する。また、ランクを計算するための処理が追加されているにもかかわらず、シミュレーション時間に関して深刻な増加はみられなかった。変更後のシミュレーション速度も、ほぼ 1.1MIPS である。理想的な IPC の測定結果を見ると、124.m88ksim と 253.perlbmk で低い値を示したが、それ以外のベンチマークでは数十というレベルから多いもので 186.crafty の 108 という高い並列性が内在していることを確認できた。

#### 5. おわりに

プロセッサアーキテクチャ研究とプロセッサ教育における利用を目的として、プロセッサシミュレータ SimAlpha Version 1.0 を構築した。本稿では、コードの高い可読性を示すために、実際の C++のコードを示しながら SimAlpha のソフトウェアアーキテクチャを明らかにした。また、SimAlpha の利用例として、理想的な命令レベル並列性を測定する方法を示し、

表 1 SimAlpha を用いて測定した実行命令数、シミュレーション 速度、理想的な命令レベル並列性

Table 1 Instruction count, million instructions per second, and oracle instruction level parallelism measured with SimAlpha.

| Program            | instruction count | MIPS | IPC   |

|--------------------|-------------------|------|-------|

| 099.go             | 138 million       | 1.12 | 64.2  |

| 124.m88ksim        | 127 million       | 1.12 | 10.5  |

| $126.\mathrm{gcc}$ | 150 million       | 1.12 | 41.8  |

| 129.compress       | 142 million       | 1.14 | 56.6  |

| 130.li             | 208 million       | 1.11 | 20.0  |

| 132.ijpeg          | 172 million       | 1.21 | 107.0 |

| 134.perl           | 153 million       | 1.10 | 43.3  |

| 147.vortex         | 184 million       | 1.07 | 32.0  |

| 164.gzip           | 596 million       | 1.19 | 16.9  |

| 175.vpr            | 17 million        | 1.00 | 25.1  |

| $176.\mathrm{gcc}$ | 551 million       | 1.10 | 47.1  |

| 181.mcf            | 188 million       | 1.12 | 53.1  |

| 186.crafty         | 4264 million      | 1.10 | 108.0 |

| 197.parser         | 611 million       | 1.10 | 30.9  |

| 252.eon            | 94 million        | 0.93 | 49.7  |

| 253.perlbmk        | 200 million       | 1.05 | 8.4   |

| 254.gap            | 1169 million      | 1.12 | 32.1  |

| 255.vortex         | 147 million       | 1.06 | 29.3  |

| 256.bzip2          | 1819 million      | 1.12 | 43.6  |

| 300.twolf          | 91 million        | 1.00 | 21.9  |

これを測定するための機能を数十行という少ない記述 で追加できることを述べた。変更した SimAlpha を利 用して SPEC CINT95 と CINT2000 の理想的な命令 レベル並列性を測定し、その結果を報告した。

SimAlpha Version 1.0 と、理想的な命令レベル並列性を得るために変更を加えたソースコードは次のURL からダウンロードできる。

http://www.yuba.is.uec.ac.jp/~kis/SimAlpha/

謝辞 SimAlpha の初期のバージョンをテストし、 貴重なコメントやパッチを頂いた飯塚大介氏に深く感 謝致します。

#### 参考文献

- 1) Doug Burger and Todd M. Austin: The Simplescalar Tool Set, Version 2.0, Technical Report CS-TR-1997-1342, University of Wisconsin, Madison (1997).

- Monica S. Lam and Robert P. Wilson: Limits of Control Flow on Parallelism, 19th Annual International Symposium on Computer Architecture, pp. 46–57 (1992).

- R. E. Kessler: The Alpha 21264 Microprocessor, *IEEE Micro*, Vol. 19, No. 2, pp. 25–36 (1999).

- Shubhendu S. Mukherjee, Sarita V. Adve, Todd Austin, Joel Emer and Peter S. Magnusson: Performance Simulation Tools, *IEEE Computer*, Vol. 35, No. 2, pp. 38–39 (2002).