M-Coreアーキテクチャは実用的で理解しやすいメニーコアアーキテクチャである. 以下に述べるコンセプトに基づいて開発を行っている.

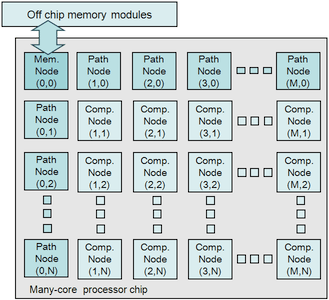

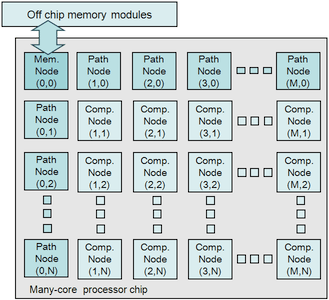

図に示すように多数のノードをタイル上に配置するタイルアーキテクチャを採用する. 各ノードはチップ内の2次元メッシュネットワークで接続される. 各ノードにはチップ内で固有のノードID を割り当てる. ノードID は,ノード間でデータを通信する際に,ノードを指定するために使用する. ノードID はチップ上のX座標とY座標の組合せで表現する. ノードID が(X,Y)となるノードをNode(X,Y)と表記する. ノードには,計算ノード,メモリノード,パスノードの3種類がある. 計算ノードは,コアを格納し,アプリケーションプログラムの実行およびパケットの転送をおこなう. メモリノードはオフチップのメインメモリに接続し, 計算ノードとメインメモリのインターフェイスの役割を果たす. パスノードは主にパケットの転送をおこなう. 図において,計算ノードがNode(1,1) からNode (M,N),メモリノードがNode(0,0), パスノードがNode(1,0)からNode(M,0)およびNode(0,1)からNode(0,N)である.

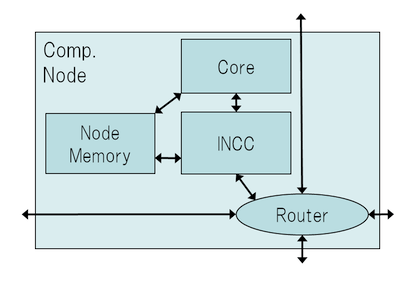

上の図に計算ノードのブロック図を示す. 計算ノードは,コア,ノードメモリ,INCC(Inter Node Communication Controller), ルータで構成される.コアは軽量化したプロセッシングエレメントである. ノードメモリは小規模なローカルメモリである. ノードメモリには,プログラムの実行に必要な命令およびデータを格納する. INCC は,ノード間の通信を扱うコントローラである. また,ルータは,隣接する4 つのノードのルータおよび自身のノードのINCC の5 方向と接続し, パケットを転送する.

パケットの送受信にはDMA (Direct Memory Access) を利用する. これを用いて,自身のノードメモリにあるデータを他の計算ノードのノードメモリまたはメモリノードのメインメモリに複製する.

パケットのルーティング方式には, 構成がシンプルであるXY 次元順ルーティングを採用する. この方式では,パケットはまずX軸方向に転送され,次にY軸方向に転送される. また,パケットはフリットに分割され,パイプライン式に転送される

コアの命令セットアーキテクチャはプロセッサアーキテクチャの教育・研究において多くの実績があるMIPS32 を採用する. 浮動小数点演算をサポートする. 割り込み制御機構は備えない. マイクロアーキテクチャの複雑化を避けるために, シングルサイクルのプロセッサを採用する.

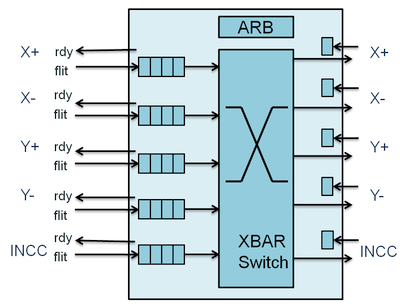

図にルータのマイクロアーキテクチャを示す. パケットは入力線を経由して入力バッファに格納され, XBAR switchを通り,適切な方向へと出力される. 各入出力ポートは1フリット分のビット幅を備える. Arbiterがラウンドロビン方式でパケットの調停を行う. 入力バッファはFIFOであり,最大4フリットを格納する領域を備える.

Copyright(c) 2010, Tokyo Tech Kise Laboratory. All rights reserved.