Fiscal Year 2023

Ver. 2023-12-10a

Course number: CSC.T433 School of Computing, Graduate major in Computer Science

# Advanced Computer Architecture

# 2. Instruction Set Architecture and single-cycle processor

www.arch.cs.titech.ac.jp/lecture/ACA/ Room No.W834, Lecture (Face-to-face) Mon 13:30-15:10, Thr 13:30-15:10

Kenji Kise, Department of Computer Science kise \_at\_ c.titech.ac.jp

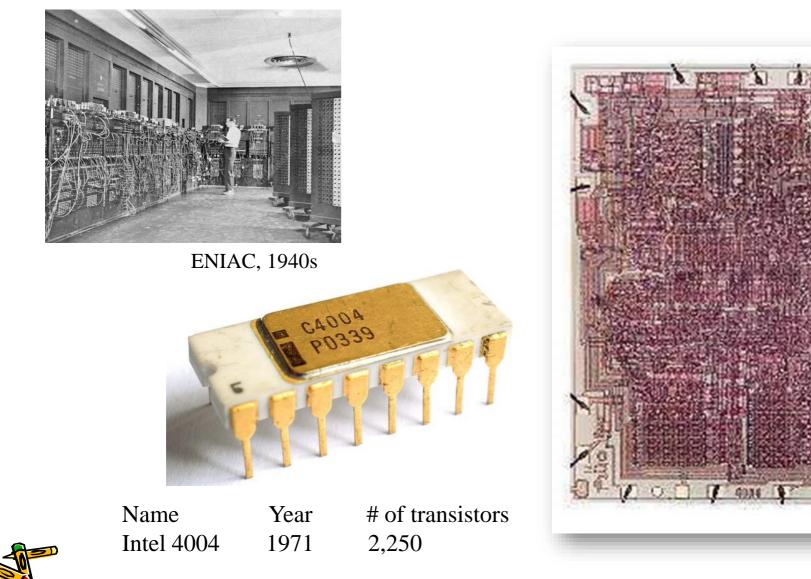

# The birth of microprocessors in 1971

#### Discussion: software and hardware

```

#include <stdio.h>

main()

{

printf("hello, world¥n");

}

```

Hardware to light up some LEDs

### Two major ISA types: RISC vs CISC

- RISC (Reduced Instruction Set Computer) philosophy

- fixed instruction lengths

- load-store instruction sets

- limited addressing modes

- limited operations

- RISC: MIPS, Alpha, ARM, RISC-V, ...

- CISC (Complex Instruction Set Computer) philosophy

- I fixed instruction lengths

- ! load-store instruction sets

- ! limited addressing modes

- ! limited operations

- CISC : DEC VAX11, Intel 80x86, ...

## MIPS, ARM, and RISC-V

|                                                                                                                                                                                                             | https://en.wikipedia.or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | rg/wiki/MIPS_architecture                                                                                                                                                                                                                                                                                                       |                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|                                                                                                                                                                                                             | Article Talk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Read Edit View history                                                                                                                                                                                                                                                                                                          | arm                                                                                   |

| WIKIPEDIA                                                                                                                                                                                                   | MIPS architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                 | arm                                                                                   |

| The Free Encyclopedia                                                                                                                                                                                       | From Wikipedia, the free encyclopedia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                 |                                                                                       |

| Main page<br>Contents<br>Current events<br>Random article<br>About Wikipedia<br>Contact us<br>Donate<br>Contribute<br>Help<br>Community portal<br>Recent changes<br>Upload file<br>Tools<br>What links here | <ul> <li>MIPS (Microprocessor without Interlocked Pipelined Stages)<sup>[1]</sup> is a reduced in instruction set architecture (ISA)<sup>[2]:A-1[3]:19</sup> developed by MIPS Computer Systems United States.</li> <li>There are multiple versions of MIPS: including MIPS I, II, III, IV, and V; as well as 64-bit implementations, respectively). The early MIPS architectures were 32-bit on later. As of April 2017, the current version of MIPS is MIPS32/64 Release 6.<sup>[4][5]</sup> M V by defining the privileged kernel mode System Control Coprocessor in addition to The MIPS architecture has several optional extensions. MIPS-3D which is a simple : dedicated to common 3D tasks,<sup>[6]</sup> MDMX (MaDMaX) which is a more extensive inte bit floating-point registers, MIPS16e which adds compression to the instruction stre room,<sup>[7]</sup> and MIPS MT, which adds multithreading capability.<sup>[8]</sup></li> <li>Computer architecture courses in universities and technical schools often study the greatly influenced later RISC architectures such as Alpha.</li> </ul> | s, now MIPS Technologies, based in the<br>five releases of MIPS32/64 (for 32- and<br>Ily; 64-bit versions were developed<br>IPS32/64 primarily differs from MIPS I-<br>o the user mode architecture.<br>set of floating-point SIMD instructions<br>eger SIMD instruction set using the 64-<br>eam to make programs take up less | Arm "ABCD" building in Cherry Hinton,<br>Cambridge, UK<br>ARM (Advanced RISC Machine) |

|                                                                                                                                                                                                             | RISC-V°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | About RISC-V 🗸 Membership 🖌 RISC-V Exc                                                                                                                                                                                                                                                                                          | hange Technical ~ News & Events ~ Community ~ Q                                       |

|                                                                                                                                                                                                             | RISC-V is an open standard Instruction Set<br>(ISA) enabling a new era of processor in<br>through open collaboration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | History of RISC-V > ISC-V Are y<br>Board of Directors                                                                                                                                                                                                                                                                           | /ou ready to break free?                                                              |

|                                                                                                                                                                                                             | RISC-V enables the community to share technical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Technical Steering<br>Committee                                                                                                                                                                                                                                                                                                 |                                                                                       |

|                                                                                                                                                                                                             | contribute to the strategic future, create more ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RISC-V Staff                                                                                                                                                                                                                                                                                                                    |                                                                                       |

|                                                                                                                                                                                                             | unprecedented design freedom, and substantially re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Guidelines >                                                                                                                                                                                                                                                                                                                    |                                                                                       |

Frequently Asked Questions

Contact Us

RISC-V International is the global non-profit home of the open standard RISC-V Instruction Set Architecture (ISA), related specifications, and stakeholder community

innovation

3,950 RISC-V members across 70 countries contribute and collaborate to define RISC-V open specifications as well as convene and govern related technical, industry, domain, and special interest groups.

#### Understanding the RISC-V ISA Open Standard

At the base level, the RISC-V ISA and extensions ratified by RISC-V International are royalty free and open base building blocks for anyone to build their own solutions and services on. The RISC-V ISA and ratified extensions are provided under globally accepted open licenses that are permanently open and remain available for all.

Beyond RISC-V International, the community has opportunity to provide their own free or

https://riscv.org/

CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

#### **RISC-V** base and extensions

#### **Chapter 1**

#### FE310-G002 Description

#### 1.1 Features

- SiFive E31 Core Complex up to 320MHz.

- Flexible clocking options including internal PLL, free-running ring oscillator and external 16MHz crystal.

- 1.61 DMIPs/MHz, 2.73 Coremark/MHz

#### RV32IMAC

- 8kB OTP Program Memory

- 8kB Mask ROM

- 16kB Instruction Cache

- 16kB Data SRAM

- 3 Independent PWM Controllers

- External RESET pin

- · JTAG, SPI I2C, and UART interfaces.

- QSPI Flash interface.

- Requires 1.8V and 3.3V supplies.

- · Hardware Multiply and Divide

#### 1.2 Description

The FE310-G002 is the second Freedom E300 SoC. The FE310-G002 is built around the E31 Core Complex instantiated in the Freedom E300 platform.

The FE310-G002 Manual should be read together with this datasheet. This datasheet provides electrical specifications and an overview of the FE310-G002.

The FE310-G002 comes in a convenient, industry standard 6x6mm 48-lead QFN package ( 0.4mm pad pitch ).

|          | ISA base and extensions (20191213)                                 |         |                       |  |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------|---------|-----------------------|--|--|--|--|--|--|--|

| Name     | Description                                                        | Version | Status <sup>[a]</sup> |  |  |  |  |  |  |  |

|          | Base                                                               |         |                       |  |  |  |  |  |  |  |

| RVWMO    | Weak Memory Ordering                                               | 2.0     | Ratified              |  |  |  |  |  |  |  |

| RV32I    | Base Integer Instruction Set, 32-bit                               | 2.1     | Ratified              |  |  |  |  |  |  |  |

| RV32E    | Base Integer Instruction Set (embedded), 32-bit, 16 registers      | 1.9     | Open                  |  |  |  |  |  |  |  |

| RV64I    | Base Integer Instruction Set, 64-bit                               | 2.1     | Ratified              |  |  |  |  |  |  |  |

| RV128I   | Base Integer Instruction Set, 128-bit                              | 1.7     | Open                  |  |  |  |  |  |  |  |

|          | Extension                                                          |         |                       |  |  |  |  |  |  |  |

| М        | Standard Extension for Integer Multiplication and Division         | 2.0     | Ratified              |  |  |  |  |  |  |  |

| A        | Standard Extension for Atomic Instructions                         | 2.1     | Ratified              |  |  |  |  |  |  |  |

| F        | Standard Extension for Single-Precision Floating-Point             | 2.2     | Ratified              |  |  |  |  |  |  |  |

| D        | Standard Extension for Double-Precision Floating-Point             | 2.2     | Ratified              |  |  |  |  |  |  |  |

| G        | Shorthand for the base integer set (I) and above extensions (MAFD) | N/A     | N/A                   |  |  |  |  |  |  |  |

| Q        | Standard Extension for Quad-Precision Floating-Point               | 2.2     | Ratified              |  |  |  |  |  |  |  |

| L        | Standard Extension for Decimal Floating-Point                      | 0.0     | Open                  |  |  |  |  |  |  |  |

| С        | Standard Extension for Compressed Instructions                     | 2.0     | Ratified              |  |  |  |  |  |  |  |

| В        | Standard Extension for Bit Manipulation                            | 0.92    | Open                  |  |  |  |  |  |  |  |

| J        | Standard Extension for Dynamically Translated Languages            | 0.0     | Open                  |  |  |  |  |  |  |  |

| т        | Standard Extension for Transactional Memory                        | 0.0     | Open                  |  |  |  |  |  |  |  |

| Р        | Standard Extension for Packed-SIMD Instructions                    | 0.2     | Open                  |  |  |  |  |  |  |  |

| V        | Standard Extension for Vector Operations                           | 0.9     | Open                  |  |  |  |  |  |  |  |

| N        | Standard Extension for User-Level Interrupts                       | 1.1     | Open                  |  |  |  |  |  |  |  |

| н        | Standard Extension for Hypervisor                                  | 0.4     | Open                  |  |  |  |  |  |  |  |

| ZiCSR    | Control and Status Register (CSR)                                  | 2.0     | Ratified              |  |  |  |  |  |  |  |

| Zifencei | Instruction-Fetch Fence                                            | 2.0     | Ratified              |  |  |  |  |  |  |  |

| Zam      | Misaligned Atomics                                                 | 0.1     | Open                  |  |  |  |  |  |  |  |

| Ztso     | Total Store Ordering                                               | 0.1     | Frozen                |  |  |  |  |  |  |  |

#### RISC-V RV32I base and our target instructions

|              | RV32I                                  | Base Instru | action S | $\mathbf{et}$ |         |          |

|--------------|----------------------------------------|-------------|----------|---------------|---------|----------|

|              | imm[31:12]                             |             |          | rd            | 0110111 | ] LUI    |

|              | imm[31:12]                             |             |          | rd            | 0010111 | AUIPC    |

| imi          | n[20 10:1 11 19                        | 9:12]       |          | rd            | 1101111 | JAL      |

| imm[11:      | 0]                                     | rs1         | 000      | rd            | 1100111 | JALR     |

| imm[12 10:5] | rs2                                    | rs1         | 000      | imm[4:1 11]   | 1100011 | BEQ      |

| imm[12 10:5] | rs2                                    | rs1         | 001      | imm[4:1 11]   | 1100011 | BNE      |

| imm[12 10:5] | rs2                                    | rs1         | 100      | imm[4:1 11]   | 1100011 | BLT      |

| imm[12 10:5] | rs2                                    | rs1         | 101      | imm[4:1 11]   | 1100011 | BGE      |

| imm[12 10:5] | rs2                                    | rs1         | 110      | imm[4:1 11]   | 1100011 | BLTU     |

| imm[12 10:5] | rs2                                    | rs1         | 111      | imm[4:1 11]   | 1100011 | BGEU     |

| imm[11:      |                                        | rs1         | 000      | rd            | 0000011 | ] LB     |

| imm[11:      |                                        | rs1         | 001      | rd            | 0000011 | ] LH     |

| imm[11:      | 0]                                     | rs1         | 010      | rd            | 0000011 | LW       |

| imm[11:      | 0]                                     | rs1         | 100      | rd            | 0000011 | LBU      |

| imm[11:      | 0]                                     | rs1         | 101      | rd            | 0000011 | LHU      |

| imm[11:5]    | rs2                                    | rs1         | 000      | imm[4:0]      | 0100011 | ] SB     |

| imm[11:5]    | rs2                                    | rs1         | 001      | imm[4:0]      | 0100011 | ] SH     |

| imm[11:5]    | rs2                                    | rs1         | 010      | imm[4:0]      | 0100011 | SW       |

| imm[11:      | 0]                                     | rs1         | 000      | rd            | 0010011 | ADDI     |

| L            | 1                                      | rs1         | 010 011  | rd            | 0010011 | SLTI     |

|              | $rac{11:0]}{11:0]}$<br>11:0]<br>11:0] |             |          | rd            | 0010011 | SLTIU    |

|              | L ]                                    |             | 100      | rd            | 0010011 | XORI     |

| imm[11:      | 0]                                     | rs1         | 110      | rd            | 0010011 | ORI      |

| imm[11:      | 1                                      | rs1         | 111      | rd            | 0010011 | ANDI     |

| 0000000      | shamt                                  | rs1         | 001      | rd            | 0010011 | ] SLLI   |

| 0000000      | shamt                                  | rs1         | 101      | rd            | 0010011 | SRLI     |

| 0100000      | shamt                                  | rs1         | 101      | rd            | 0010011 | SRAI     |

| 0000000      | rs2                                    | rs1         | 000      | rd            | 0110011 | ADD      |

| 0100000      | rs2                                    | rs1         | 000      | rd            | 0110011 | SUB      |

| 0000000      | rs2                                    | rs1         | 001      | rd            | 0110011 | ] SLL    |

| 0000000      | rs2                                    | rs1         | 010      | rd            | 0110011 | SLT      |

| 0000000      | rs2                                    | rs1         | 011      | rd            | 0110011 | SLTU     |

| 0000000      | rs2                                    | rs1         | 100      | rd            | 0110011 | XOR      |

| 0000000      | rs2                                    | rs1         | 101      | rd            | 0110011 | SRL      |

| 0100000      | rs2                                    | rs1         | 101      | rd            | 0110011 | ] SRA    |

| 0000000      | rs2                                    | rs1         | 110      | rd            | 0110011 | OR       |

| 0000000      |                                        |             | rd       | 0110011       |         |          |

| fm pre       |                                        | rs1         | 000      | rd            | 0001111 | FENCE    |

| 00000000     |                                        | 00000       | 000      | 00000         | 1110011 | ECALL    |

| 00000000     | 001                                    | 00000       | 000      | 00000         | 1110011 | ] EBREAK |

## RISC-V general-purpose registers

0

XLEN-1

#### XLEN = 32 for 32bit ISA

| XLEN-1 |           | 0 |

|--------|-----------|---|

|        | x0 / zero |   |

|        | x1        |   |

|        | x2        |   |

|        | x3        |   |

|        | x4        |   |

|        | x5        |   |

|        | x6        |   |

|        | x7        |   |

|        | x8        |   |

|        | x9        |   |

|        | x10       |   |

|        | x11       |   |

|        | x12       |   |

|        | x13       |   |

|        | x14       |   |

|        | x15       |   |

|        | x16       |   |

|        | x17       |   |

|        | x18       |   |

|        | x19       |   |

|        | x20       |   |

|        | x21       |   |

|        | x22       |   |

|        | x23       |   |

|        | x24       |   |

|        | x25       |   |

|        | x26       |   |

|        | x27       |   |

|        | x28       |   |

|        | x29       |   |

|        | x30       |   |

|        | x31       |   |

|        | XLEN      |   |

| XLEN-1 |           | 0 |

|        | pc        |   |

|        | XLEN      |   |

#### ABI(Application Binary Interface) name

| Register | ABI Name | Description                      | Saver  |

|----------|----------|----------------------------------|--------|

| x0       | zero     | Hard-wired zero                  | —      |

| x1       | ra       | Return address                   | Caller |

| x2       | sp       | Stack pointer                    | Callee |

| x3       | gp       | Global pointer                   |        |

| x4       | tp       | Thread pointer                   |        |

| x5–7     | t0-2     | Temporaries                      | Caller |

| x8       | s0/fp    | Saved register/frame pointer     | Callee |

| x9       | s1       | Saved register                   | Callee |

| x10-11   | a0-1     | Function arguments/return values | Caller |

| x12–17   | a2–7     | Function arguments               | Caller |

| x18–27   | s2–11    | Saved registers                  | Callee |

| x28–31   | t3-6     | Temporaries                      | Caller |

| f0-7     | ft0-7    | FP temporaries                   | Caller |

| f8-9     | fs0-1    | FP saved registers               | Callee |

| f10-11   | fa0-1    | FP arguments/return values       | Caller |

| f12-17   | fa2-7    | FP arguments                     | Caller |

| f18-27   | fs2-11   | FP saved registers               | Callee |

| f28-31   | ft8-11   | FP temporaries                   | Caller |

Table 18.2: RISC-V calling convention register usage.

CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

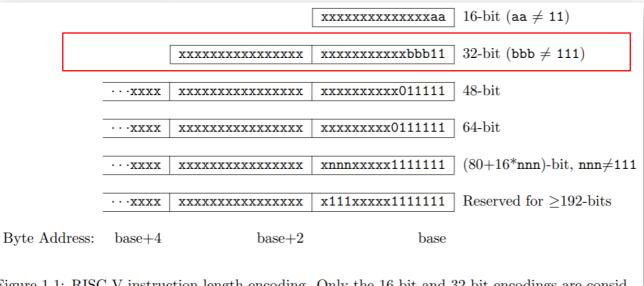

### RISC-V instruction length encoding

The RISC-V Instruction Set Manual Volume I: Unprivileged ISA Document Version 20191214-draft

Editors: Andrew Waterman<sup>1</sup>, Krste Asanović<sup>1,2</sup> <sup>1</sup>SiFive Inc., <sup>2</sup>CS Division, EECS Department, University of California, Berkeley andrew@sifive.com, krste@berkeley.edu November 12, 2021

Figure 1.1: RISC-V instruction length encoding. Only the 16-bit and 32-bit encodings are considered frozen at this time.

#### **RISC-V** base instruction format

| 31 30 25                | 24 21 20     | 19  | 15 14 12  | 2 11 8 7         | 6 0    | _            |

|-------------------------|--------------|-----|-----------|------------------|--------|--------------|

| funct7                  | rs2          | rs1 | funct3    | rd               | opcode | ] R-type     |

| • [1                    | 1.0]         | 1   |           | 1                | 1      | ] <b>т</b> ( |

| imm[1                   | 1:0]         | rs1 | funct3    | rd               | opcode | ] I-type     |

| :                       |              |     | free at 9 | :                |        |              |

| imm[11:5]               | rs2          | rs1 | funct3    | imm[4:0]         | opcode | S-type       |

| [imm[12]] $[imm[10:5]]$ | rs2          | rs1 | funct3    | imm[4:1] imm[11] | opcode | B-type       |

|                         | 152          | 151 | Tuneto    |                  | opcouc | D-type       |

|                         | imm[31:12]   |     |           | rd               | opcode | U-type       |

| L                       | L ]          |     |           | 1                | -      |              |

| [imm[20]] $imm[1]$      | 0:1] imm[11] | imm | [19:12]   | rd               | opcode | ] J-type     |

Figure 2.3: RISC-V base instruction formats showing immediate variants.

## **RISC-V** Arithmetic Instructions

• RISC-V assembly language arithmetic statement

add x7, x8, x9 sub x7, x8, x9

- Each arithmetic instruction performs only one operation

- Each arithmetic instruction fits in 32 bits and specifies exactly three operands

destination <- source1 op source2</pre>

- Operand order is fixed (destination first)

- Those operands are all contained in the datapath's register file (x0, ..., x31)

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005 CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

### Exercise 1

• Compiling a C assignment using registers

f = ( g + h ) - ( i + j );

The variables f, g, h, i, and j are assigned to the registers s0, s1, s2, s3, and s4, respectively. What is the compiled RISC-V code?

Register ABI Name Description x0 zero Hard-wired zero

s0 = (s1 + s2) - (s3 + s4);

t0 = s1 + s2; t1 = s3 + s4; s0 = t0 - t1;

| Register | ABI Name | Description                      | Saver  |

|----------|----------|----------------------------------|--------|

| x0       | zero     | Hard-wired zero                  |        |

| x1       | ra       | Return address                   | Caller |

| x2       | sp       | Stack pointer                    | Callee |

| x3       | gp       | Global pointer                   |        |

| x4       | tp       | Thread pointer                   | _      |

| x5–7     | t0-2     | Temporaries                      | Caller |

| x8       | s0/fp    | Saved register/frame pointer     | Callee |

| x9       | s1       | Saved register                   | Callee |

| x10-11   | a0–1     | Function arguments/return values | Caller |

| x12–17   | a2–7     | Function arguments               | Caller |

| x18–27   | s2–11    | Saved registers                  | Callee |

| x28–31   | t3-6     | Temporaries                      | Caller |

| f0-7     | ft0-7    | FP temporaries                   | Caller |

| f8-9     | fs0-1    | FP saved registers               | Callee |

| f10-11   | fa0-1    | FP arguments/return values       | Caller |

| f12-17   | fa2-7    | FP arguments                     | Caller |

| f18-27   | fs2-11   | FP saved registers               | Callee |

| f28-31   | ft8-11   | FP temporaries                   | Caller |

Table 18.2: RISC-V calling convention register usage.

# (1) Machine Language - Add instruction (add)

- Instructions are 32 bits long

- Arithmetic Instruction Format (R-type):

add x7, x8, x9

| funct7 | rs2 | rs1 | funct3 | rd | opcode | R-type |

|--------|-----|-----|--------|----|--------|--------|

|--------|-----|-----|--------|----|--------|--------|

opcode 7-bits opcode that specifies the operation

- rs1 5-bits register file address of the first source operand

- rs2 5-bits register file address of the second source operand

- rd 5-bits register file address of the result's destination

funct3 and funct7 10-bits select the type of operation (function)

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005 CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

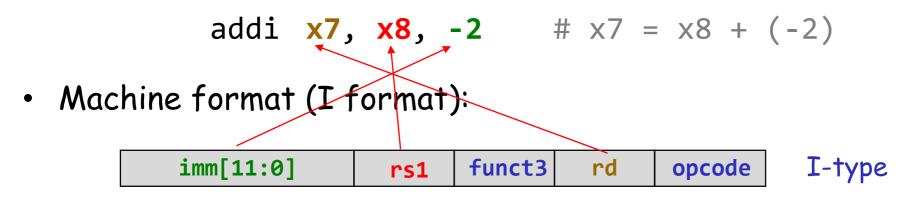

# (2) RISC-V Add immediate instruction (addi)

- Small constants are used often in typical code

- Possible approaches?

- put "typical constants" in memory and load them

- create hard-wired registers (like x0) for constants like 1

- have special instructions that contain constants !

- The constant is kept inside the instruction itself

- Immediate format limits values to the range +2<sup>11</sup>-1 to -2<sup>11</sup>

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005 CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

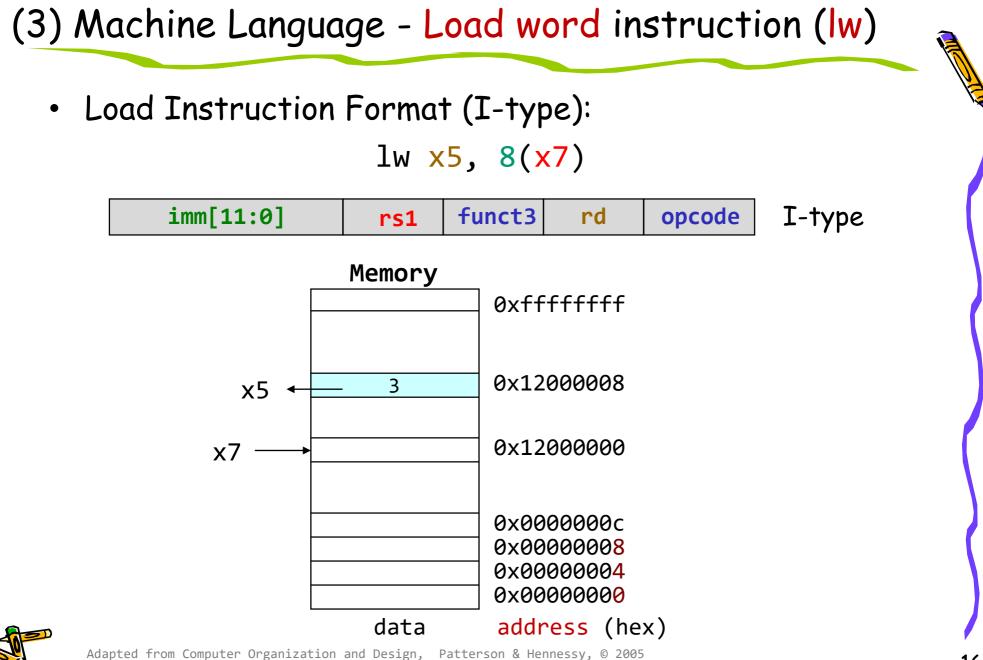

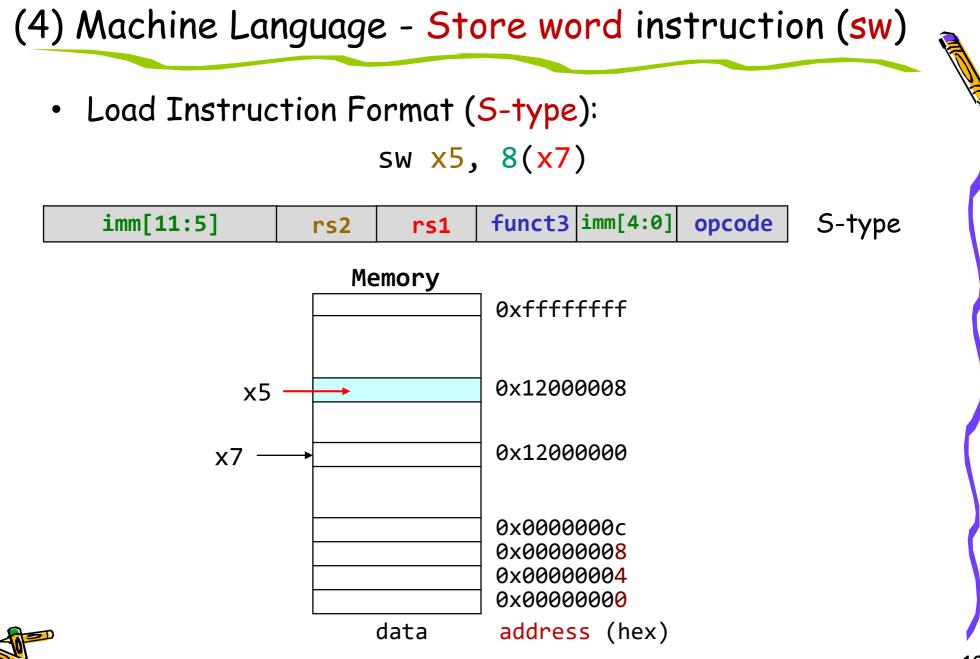

#### **RISC-V** Memory Access Instructions

- RISC-V has two basic data transfer instructions for accessing memory

- lw x5, 24(x7) # load word from memory

- sw  $\times 3$ , 28(x9) # store word to memory

- The data is loaded into (lw) or stored from (sw) a register in the register file

- The memory address a 32 bit address is formed by adding the contents of the base address register to the offset value

### Exercise 2

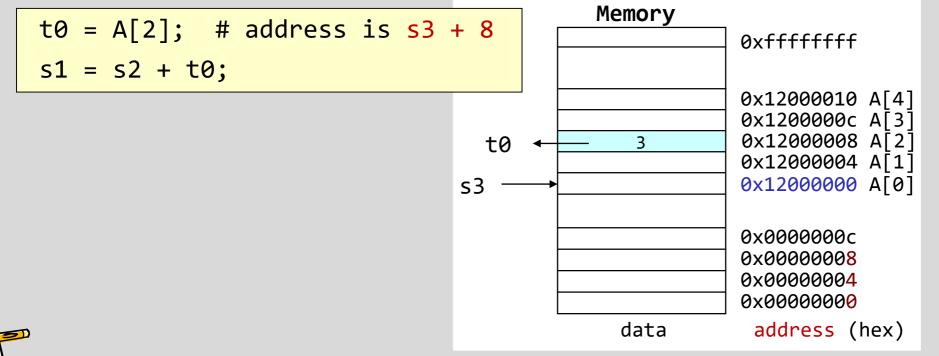

• Compiling an assignment when an operand is in memory

g = h + A[2];

Let's assume that A is an array of 100 words and the compiler has associated the variable g and h with the registers s1 and s2 as before. Let's also assume that the starting address, or base address, of the array is in s3. Compile this C assignment statement.

#### Exercise 3

• Compiling using load and store

A[1] = h + A[2];

• Assume variable h is associated with register s2 and base address of the array A is in s3. What is the RISC-V assembly code for the C assignment statement?

```

t0 = A[2]; # address is s3 + 8

t1 = s2 + t0;

A[1] = t1; # address is s3 + 4

```

## (5) RISC-V branch if not equal instructions (bne)

RISC-V conditional branch instructions (bne, branch if not equal):

bne x4, x5, Lbl # go to Lbl if x4!=x5

Ex: if

$$(i==j) h = i + j;$$

bne x4, x5, Lbl1 # if (i!=j) goto Lbl1

add x6, x4, x5 # h = i + j;

Lbl1: ...

Instruction Format (B-type):

$\operatorname{imm}[12] | \operatorname{imm}[10:5] | rs2 | rs1 | \operatorname{funct3} | \operatorname{imm}[4:1] | \operatorname{imm}[11] | \operatorname{opcode} | B-type$

• How is the branch destination address specified?

Adapted from Computer Organization and Design, Patterson & Hennessy, © 2005 CSC.T433 Advanced Computer Architecture, Department of Computer Science, TOKYO TECH

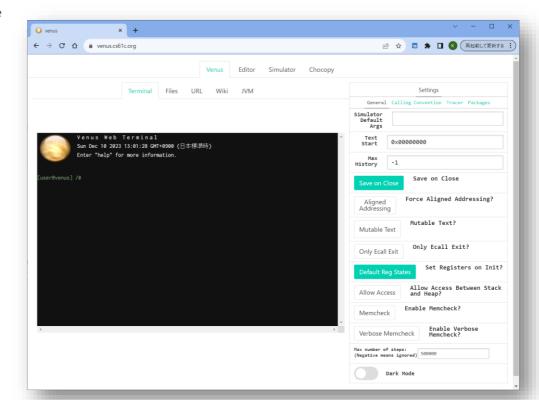

## Venus RISC-V editor and simulator will help us

https://github.com/kvakil/venus

#### Features

- RV32IM

- Single-step debugging with undo feature

- Breakpoint debugging

- View machine code and original instructions side-by-side

- Several ecall s: including print and sbrk

- Memory visualization

https://venus.cs61c.org/

#### Exercise 4

• Compiling using add, addi, and bne

```

void main(){

int i, sum=0;

for(i=1; i<11; i++) sum = sum + i;

}</pre>

```

What is the RISC-V assembly code for the C assignment statement?

```

void main(){

int s2, s3=11, s4=0;

for(s2=1; s2<s3; s2++) s4 = s4 + s2;

}</pre>

```

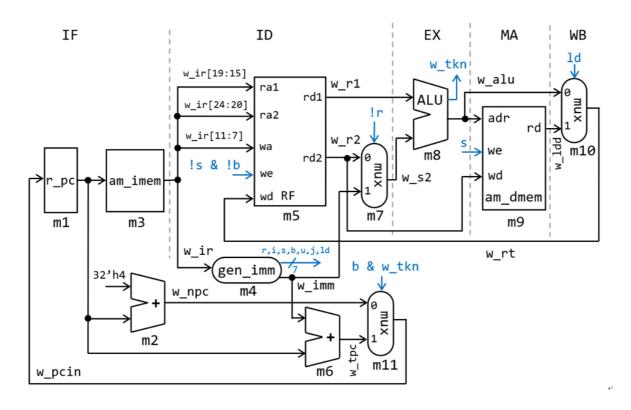

### Single-cycle implementation of processors

Single-cycle implementation also called single clock cycle implementation is the implementation in which an instruction is executed in one clock cycle. While easy to understand, it is too slow to be practical.

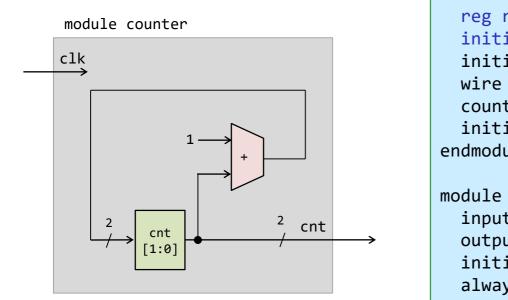

# Sample circuit 3

• 2-bit counter as a simple sequential circuit

```

module top();

reg r_clk=0;

initial #150 forever #50 r_clk = ~r_clk;

initial #810 $finish;

wire [1:0] w_cnt;

counter m1 (r_clk, w_cnt);

initial $dumpvars(0, m1);

endmodule

module counter(clk, cnt);

input wire clk;

output reg [1:0] cnt;

initial cnt = 0;

```

```

always@(posedge clk) cnt <= cnt + 1;

endmodule

```

| Signals  | Waves |     |        |       |     |     |     |     |     |     |     |     |     |     |        |

|----------|-------|-----|--------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| Time     |       | 100 | sec 20 | ) sec | 300 | sec | 400 | sec | 500 | sec | 600 | sec | 700 | sec | 800 se |

| clk      |       |     |        |       | 1   |     | 1   |     |     |     |     |     | 1   |     |        |

| cnt[1:0] | 00    |     |        | 01    |     | 10  |     | 11  |     | 00  |     | 01  |     | 10  |        |

|          |       |     |        |       |     |     |     |     |     |     |     |     |     |     |        |