The 1st IPSJ SIG-ARC High-Performance Processor Design Contest

2014年1月に東工大にて開催予定の情報処理学会計算機アーキテクチャ研究会

200回記念研究会のイベントとして,プロセッサ設計コンテスト

(リーフレット)を実施します.

高性能プロセッサ(高性能計算機システム)の設計にチャレンジしてください.

ニュース

- 決勝の結果を公開しました.受賞チームのみなさま,おめでとうございます.(2014/1/28)

- 決勝のための設計データの提出方法を公開しました.(2013/12/17)

- 予選のデータセットを公開しました.賞品情報を追加しました.(2013/12/10)

- 予選結果を公開しました.(2013/12/08)

- 参加登録の締切を12月5日午後5時まで延長しました.(2013/12/04)

- 予選のための設計データの提出方法を公開しました.(2013/12/1)

- 参加登録チームの情報を公開しました.(2013/11/30)

- アプリケーションプログラムとソフトウェア開発キットを更新(Version 1.0.1)しました.(2013/11/24)

- スライドおよびドキュメントを更新しました.(2013/11/12)

- コンテストルールおよびツールキットを公開しました.(2013/10/15)

- 参加登録を開始しました.(2013/10/11)

- 本ホームページを公開しました.(2013/08/30)

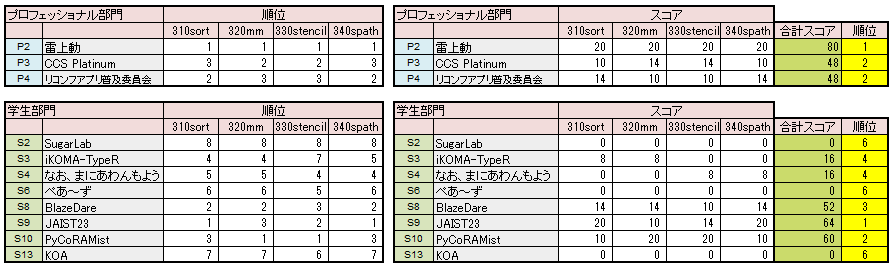

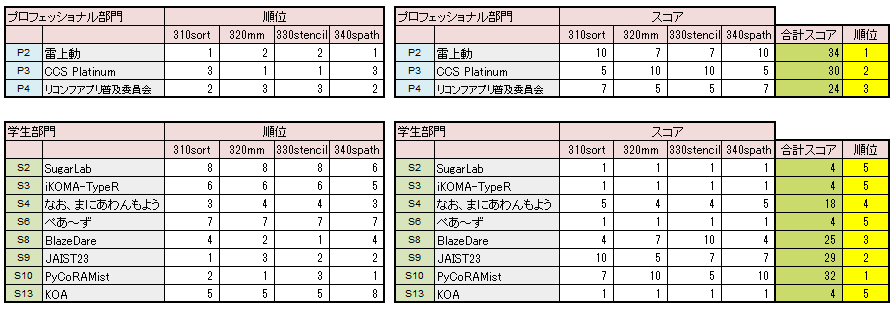

【決勝結果】

各部門の優秀チームは次の通りです.おめでとうございます.

- プロフェッショナル部門 優勝: チーム 雷上動,藤田晃史(東京大学), 塩谷亮太(名古屋大学, 中島潤(東京大学), 早水光(東京大学)

- 学生部門 優勝: チーム JAIST23, XIE, Fengxiang(北陸先端科学技術大学院大学)

- 学生部門 準優勝: チーム PyCoRAMist, 高前田伸也(東京工業大学)

- 学生部門 3位: チーム BlazeDare, 眞下達(熊本大学)

決勝結果の詳細は次の通りです.

決勝で用いたデータセットと正しい出力をまとめたファイルは

こちら(kessyo_data.zip) からダウンロードできます.

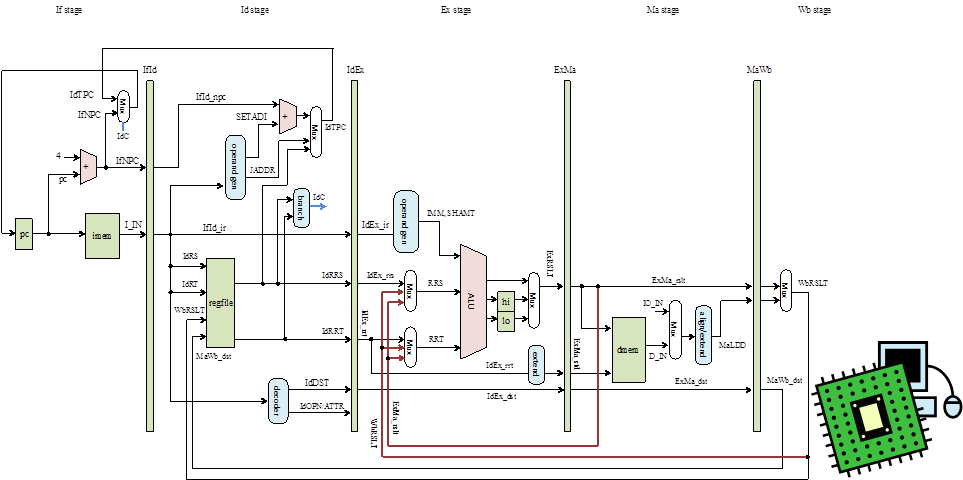

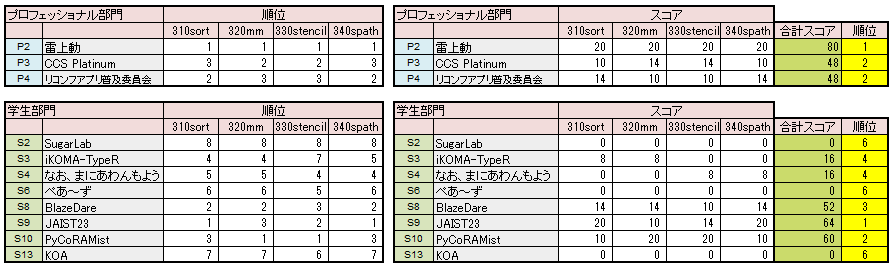

【予選結果】

予選を実施しました.P2, P3, P4, S2, S3, S4, S6, S8, S9, S10, S13 の11チームが予選通過です.おめでとうございます.

【重要】 予選通過チームは,12月9日(月)の朝から12月10日(火)13:00までに,

こちらのサイトの

発表申込メニューより,タイトル・著者情報等を登録してください.時間厳守でお願いします.

予選結果は次の通りです.

予選で用いたデータセットと正しい出力をまとめたファイルは

こちら(yosen_data.zip) からダウンロードできます.

【コンテストの趣旨】

計算機システムにおいてプロセッサは重要な役割を担っています.

また,高度な計算性能を持つPower8や豊富なインタフェースを持つスモールコアサーバなど,

その応用範囲は大きな広がりを続けています.

今後よりいっそう高度化,多様化が進む計算機の基盤技術を支える研究者,技術者の育成と交流,

研究開発の成果検証を目的に,情報処理学会 計算機アーキテクチャ研究会では,

「The 1st IPSJ SIG-ARC High-Performance Processor Design Contest(ハイパフォーマンスプロセッサ設計コンテスト)」

を開催します.

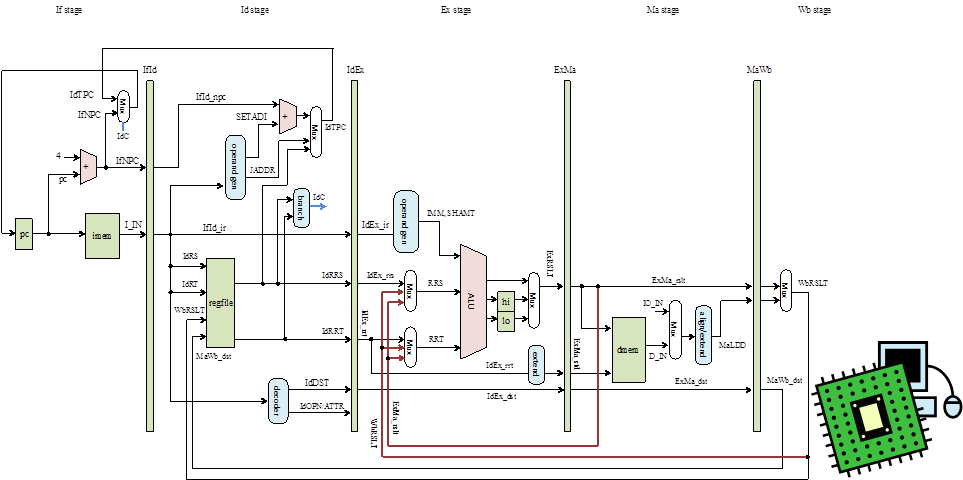

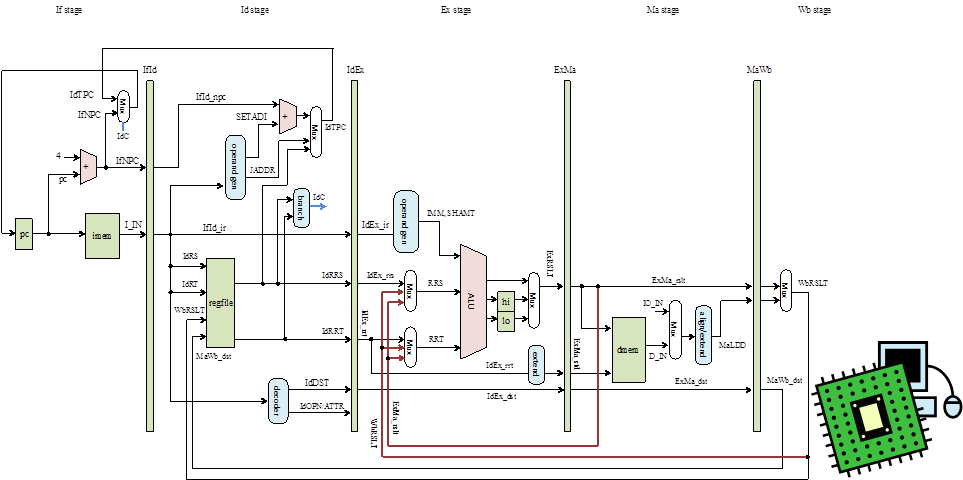

コンテストで募集する設計は,プロセッサを実装するFPGAと,

メモリ配置に関する基本的な規則以外は自由です.コンパイラ,スーパースカラ,ベクトル命令,

専用ハードウェアなど,様々なアプローチが可能です.正統派なプロセッサ技術を利用しても,

個性的で独特なアーキテクチャを提案してもOKです.

ツールキット等を提供し,参加しやすい環境を整えています.計算機科学者,

技術者の皆様の挑戦をお待ちしています!

【主催】

【協賛】

【予選のための設計データの提出方法】

予選用の設計データの提出期限は,日本標準時 2013年12月6日(金) 午後1時です.

提出するファイルは次の6種類です.これらをzipフォーマットのファイルにまとめてください.

このファイル名は yosen.zip としてください.

- FPGAの回路情報,ファイル名は System.bit としてください.

- アプリケーション 310_sort のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 310sort.bin としてください.

- アプリケーション 320_mm のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 320mm.bin としてください.

- アプリケーション 330_stencil のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 330stencil.bin としてください.

- アプリケーション 340_spath のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 340spath.bin としてください.

- 1~4ページの原稿(計算機アーキテクチャ研究会のフォーマット).PDF形式で,ファイル名は document.pdf としてください.

原稿の作成方法等は,学会Webページをご参照ください.

原稿の著者には,チーム構成員の他に,監督者あるいは指導教員を追加しても問題ありません.

設計データの提出には電子メールを用いてください.

作成したファイル yosen.zip を添付して,次の電子メールアドレスに送信してください.

電子メールのタイトルは「ハイパフォーマンスプロセッサ設計コンテスト 予選設計データ提出(チーム名)」としてください.

contest_support_at_arch.cs.titech.ac.jp (_at_ を @ に置き換えてください)

受け取った設計データを用いて,実行委員会にて動作検証をおこない,設計データ受理のメールを返信します.

正しく動作しない場合には,その旨を通知し,データの再提出を求めることがあります.

特に,設計データの提出が締切直前になる場合には,データ提出後,

12月6日(金)午後6時頃までは電子メールに直ちに返信できるように待機してください.

【決勝のための設計データの提出方法】

予選用の設計データの提出期限は,日本標準時 2013年12月20日(金) 午後1時です.

提出するファイルは次の5種類です.これらをzipフォーマットのファイルにまとめてください.

このファイル名は kessyou.zip としてください.

- FPGAの回路情報,ファイル名は System.bit としてください.

- アプリケーション 310_sort のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 310sort.bin としてください.

- アプリケーション 320_mm のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 320mm.bin としてください.

- アプリケーション 330_stencil のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 330stencil.bin としてください.

- アプリケーション 340_spath のためのユーザファイル.ファイルサイズ 256KB,ファイル名は 340spath.bin としてください.

設計データの提出には電子メールを用いてください.

作成したファイル kessyou.zip を添付して,次の電子メールアドレスに送信してください.

電子メールのタイトルは「ハイパフォーマンスプロセッサ設計コンテスト 決勝設計データ提出(チーム名)」としてください.

contest_support_at_arch.cs.titech.ac.jp (_at_ を @ に置き換えてください)

受け取った設計データを用いて,実行委員会にて動作検証をおこない,設計データ受理のメールを返信します.

正しく動作しない場合には,その旨を通知し,データの再提出を求めることがあります.

特に,設計データの提出が締切直前になる場合には,データ提出後,

12月20日(金)午後6時頃までは電子メールに直ちに返信できるように待機してください.

【コンテストルール】

- 実施形態はチーム制です.1~4人で1チームを構成して参加してください.

- 競技部門には2種類があります.適切な部門を選択して参加してください.

- 学生部門:チーム構成員の全員が学生である必要があります.

- プロフェッショナル部門: 参加条件は特にありません.

- 競技内容

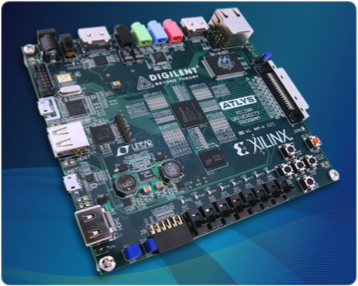

- FPGAボードは,Digilent社のAtlysボードを用います

- アプリケーションプログラムは次の4つです.

- 310_sort: 整数のソーティング

- 320_mm: 行列積,要素は整数

- 330_stencil: ステンシル計算,要素は整数

- 340_spath: 最短経路問題

- コンテストの参加者は,次のデザインを提出してください.

- 1種類のFPGAの回路情報(ファイル名は System.bit としてください)

- 4種類の実行バイナリコード(256KBのバイナリファイルを4種類)

- FPGAに実装されたプロセッサの処理時間を競います.

- 実行委員が提供するデータ(256KB)を用いて,アプリケーションプログラムの処理時間を測定し,スコアを計算します.

- 予選におけるスコアの計算方法と予選通過の条件

-

それぞれのアプリケーションについて,実行時間の短いチームから順に,

次の点数を与えます. 1位 10点,2位 7点, 3位 5点, 4位 4点

-

4種類のアプリケーションで獲得した点数の合計がスコアとなります.

-

4種類のすべてのアプリケーションが規定時間(2分とします)内に

正しい結果を出力し,かつ,合計のスコアが1点以上のチームが決勝に進出します.

-

ただし,参加チーム数等の状況により,点数を与える順位を調整することがあります.

- 決勝におけるスコアの計算方法

-

決勝では予選で獲得したスコアは考慮されません.

-

予選と決勝のアプリケーションは同じです.扱うデータは異なります.

-

それぞれのアプリケーションについて,実行時間の短いチームから順に,

次の点数を与えます. 1位 20点,2位 14点, 3位 10点, 4位 8点

-

4種類のアプリケーションで獲得した点数の合計がスコアとなります.

-

4種類のすべてのアプリケーションが規定時間(2分とします)内

に正しい結果を出力しない場合,そのチームは失格となります.

合計のスコアが多いチームが優勝となります.

- 実行時間の計測方法

-

シリアル通信にて512KBのデータ(256KBのプログラムと256KBのアプリケーションデータ)

の送信開始時刻T1から,計算結果を受け取り,最後にENDという文字列を受け取るまでの

時刻T2を実行時間(execution time) として計測します.

すなわち,execution time = T2 - T1 です.

-

シリアル通信の速度は 1M baud とします..

- 実行結果の検証

-

設計した回路は,実行委員会が提供するツールキットと全く同じ結果を出力(シリアル通信にてホスト計算機に送信)

する必要があります.また,計算結果を出力して,最後には END という文字列を出力してください.

すなわち,実行を開始してから,ホスト計算機が受信する END という文字までの全ての文字列がツールキットと

等しくなるように回路を設計してください.

【賞品】

情報処理学会 コンピュータサイエンス領域奨励賞(CS領域奨励賞)の受賞資格を満たしつつ,

優秀な性能を示すシステムを設計した2チーム以下(学生部門,プロフェッショナル部門からそれぞれ1チーム以下)に,

情報処理学会CS領域奨励賞(賞状および賞金)

を授与する予定です.

また,各部門の優勝チームには豪華賞品を贈呈する予定です.

賞品が届きました.

【参加方法】

次の注意事項をよく読んで,これらに同意される方が参加できます.

こちらのサイトから登録してください.

- 実施形態はチーム制です.1~4人で1チームを構成して参加してください.

- 競技部門には2種類があります.適切な部門を選択して参加してください.

- 学生部門:チーム構成員の全員が学生である必要があります.

- プロフェッショナル部門: 参加条件は特にありません.

- 競技内容

- FPGAボードは,Digilent社のATLYSボードを用います

- アプリケーションプログラムは次の4つです.

- コンテストの参加者は,次のデザインを提出してください.

- FPGAに実装されたプロセッサの処理時間を競います.

- 予選におけるスコアの計算方法と予選通過の条件

- 決勝におけるスコアの計算方法

- 実行時間の計測方法

- 実行結果の検証

- 設計した回路は,実行委員会が提供するツールキットと全く同じ結果を出力(シリアル通信にてホスト計算機に送信)する必要があります.また,計算結果を出力して,最後には END という文字列を出力してください.

すなわち,実行を開始してから,ホスト計算機が受信する END という文字までの全ての文字列がツールキットと等しくなるように回路を設計してください.

【環境】

本コンテストではAtlys Spartan-6 FPGA Development Boardを利用します.

この評価ボードに関する資料は

こちら

からダウンロードできます.この評価ボードは

東京エレクトロン デバイス株式会社 Academic Solution

からも購入できます.

FPGAのデザインおよびシリアル通信を用いたプログラム転送のためにWindows 7マシンの利用を推奨します.

また,MIPS命令セットのプログラムを作成するためにはMIPS用のクロス開発環境が必要になります.

このためには,

RedHat5 x86版(64ビット),CentOS6.4 x86版(32ビット),Ubuntu12.04 x86版(64ビット)

のいずれかがインストールされたLinuxマシンの利用を推奨します.

【ツールキット】

- アプリケーションプログラムとソフトウェア開発キット(SDK)

- Atlysボード用のリファレンスデザイン(512KBバイナリ転送版)

- MIPS命令セットをターゲットとするクロス開発環境(バイナリ)

- Cygwin/Linux用のバイナリ転送プログラムpsend

- Memory Image Generator memgen Version 0.9.1

【重要日程】

| 2013/09/23(月) | ツールキットお試し版(Version 0.1)の公開 |

| 2013/10/11(金) | 参加登録の開始 |

| 2013/12/05(木)午後5時(日本時間) | 参加登録の締切(延長しました) |

| 2013/12/06(金)午後1時(日本時間) | 予選デザインと原稿(1~4ページ)の提出 |

| 2013/12/10(火) | 予選結果の公表(決勝進出チームの決定) |

| 2013/12/10(火)午後1時(日本時間) | 研究会発表の登録(12月9日朝~) |

| 2013/12/12(木) | SIG-ARC研究会の原稿(1~4ページ)の提出 |

| 2013/12/20(金)午後1時(日本時間) | 決勝デザインの提出 |

| 2014/01/23(木) - 24(金) | 研究会発表,優勝者の発表(SIG-ARC研究会) |

【組織】

実行委員会

| 委員長 | 吉瀬謙二 | 東京工業大学 |

| 副委員長 | 大川猛 | 宇都宮大学 |

| 副委員長 | 吉見真聡 | 電気通信大学 |

| 荒川文男 | 名古屋大学 |

| 五島正裕 | 東京大学 |

| 佐藤寿倫 | 福岡大学 |

| 柴田裕一郎 | 長崎大学 |

| 嶋田創 | 名古屋大学 |

| 田中清史 | 北陸先端科学技術大学院大学(JAIST) |

| 津邑公暁 | 名古屋工業大学 |

| 小林諒平 | 東京工業大学 |

コンテストに関するお問い合わせは次の電子メールアドレスにお願いします.

contest_support_at_arch.cs.titech.ac.jp (_at_ を @ に置き換えてください)

Last updated: 2014/1/28 © 実行委員会